# Adaptive Neuro-Fuzzy Inference System Based BJT Model for Circuit Simulation

Kavita N. Garuku Department of Electronics Engineering Manjurkha M. Pathan Department of Electronics Engineering

#### Abstract

This paper addresses a novel approach for the modeling of Transistors based on Adaptive Neuro-Fuzzy Inference System (ANFIS). In this new approach, two phases are involved, the modeling phase and the implementation phase. The important parameters of transistor are modeled in modeling phase for which ANFIS is designed first, to represent the behavior of transistor. In the second phase, the resulting model of the transistor is then implemented using SPICE simulator. In this paper, the modeling of Transistor based on an ANFIS is presented whose main strength are that they are universal approximators with the ability to solicit interpretable IF-THEN rules. The ANFIS based model reduces the simulation time in SPICE simulators without sacrificing accuracy of physicsbased models. The results have shown that the ANFIS based device models and the simulated circuit results are in excellent agreement with the measured device and circuit.

### **1. Introduction**

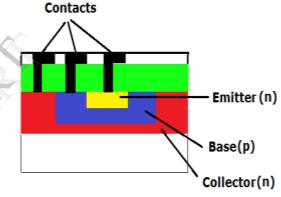

Bipolar Junction Transistor (BJT) is a three terminal semiconductor device. It is constructed from doped semiconductor material. It is a three terminal device, the three terminals named as base, emitter and collector. It is called bipolar because flow of current is due to two types of carriers; holes and electron. The flow of current is mainly due to diffusion of carriers from high concentration emitter region to base region which is in contrary to unipolar devices like field effect transistors in which flow of current is mainly due to drift of electrons or holes depending upon the type of device.

A BJT consists of three differently doped semiconductor regions emitter region, base region and collector region each having different area from one another. In PNP transistor these regions are respectively p-type, n-type and p-type whereas in NPN these regions are respectively n-type, p-type and n-type.

Figure 1. Cross section view of a npn transistor

The nature of transistor phenomenon in both the orientations is formally the same, the difference lies in the role of charge carriers. In NPN, electrons are responsible for the flow of current while in PNP, holes are the reson for the flow of current. As can be seen in fig 1. collector-base junction is much larger than emitter-base junction which is required for the proper operation of transistor.

When managing semiconductor circuits and devices, one generally deals with continuous, however extremely nonlinear, multi-dimensional dynamic systems, which makes it a tough topic, and far research is required to boost the accuracy and efficiency with which the behavior of those difficult analogue systems are often analyzed and foreseen, i.e., simulated.

Naturally, there's a nonstop push each to boost the accuracy obtained from analogue circuit simulation[1], and also to increase the capabilities for simulating very large circuits, containing several thousands of devices. These, to a large extent are conflicting necessities, since higher accuracy tends to need rather difficult models for the circuit elements, whereas higher simulation speed favors the choice of simplified, however less correct, models[2]. The latter holds, despite the final speed increase of obtainable element on which one will run the circuit simulation computer code.

Although the operation of electronic transistor is understood to us, the underlying physics for the device is a lot difficult. Therefore, simulation tools which may be applied to design these transistors in the future need new theories and modeling techniques that accurately and efficiently capture the physics[3] of these devices. Analytical models for such devices need to be utilized in circuit simulators and circuit design tools, so as to attain the desired accuracy; many authors have thoughtabout various methods for modeling the electronic transistor.

The concept of modeling a electronic transistor is based on artificial intelligence, that is, an artificial neural network (ANN) and adaptive neuro-fuzzy inference system (ANFIS) which is targeting an ANN model implementation into circuit simulator software, getting an accurate model by an ANFIS and implementing the ANFIS model into circuit simulator software like PSPICE may be a challenge, conjointly speed may be a vital factor in circuit simulations which may be simply achieved by using the proposed ANFIS model.

For discrete bipolar devices there's a significant downside of parasitic inductances and capacitances because of packaging technology (at high frequencies). Neural modeling isn't hampered by any difficult causes of behavior: it simply concerns the accurate representation of behavior, which is suitable for analogue circuit simulation.

## 2. Development of device models

## 1. Methods

Basically, there are two major reasons for determining a model of a system under investigation. One method is based on physical laws[1] involved in the system and the other is based on an analysis of the input output data[4] of the system. In practice, it is actually difficult to obtain a satisfactorily mathematical model for the system; derived using the first method, since it involves nonlinear characteristics of the system. The second method is totally based on an experimental study[5] where the data of input output signals of the system are collected and analyzed to develop a model. This method could accommodate the inherent nonlinear characteristics of the system. Hence, because of the complexity and time consuming nature of the quantum calculations for implementation in SPICE-type circuit simulators, it has been necessary to simulate the quantum mechanical model with high speed and accuracy. The ANFIS is used to provide a general link between measurements or device simulations and circuit simulation.

## 2. Modeling Categories

The device models describe the terminal behavior of a device in terms of current-voltage (I-V), capacitance-voltage (C-V) characteristics, and the carrier transport process which takes place within the device. Thus they reflect the device behavior in all regions of operation of the device. We can divide these models into two major categories:

(1) physical device models, and

(2) equivalent circuit models.

## 1. Physical Device Models

Physical device models are based on device geometry, doping profile, carrier transport equations (*semiconductor equations*) and material characteristics. These models can be used to predict both terminal characteristics and transport phenomenon. Device simulators like PISCES[6] and CADDETH[7] are used to study device design and device physics. It basically deals with solving complex two dimensional and three dimensional equations by numerical method.

## 2. Equivalent Circuit Models

Equivalent circuit models basically describe the electrical behavior of the device. It is usually done by connecting electrical circuit elements in such a way that the model emulates the electrical terminal behavior of the device. These models are thus based on the device characteristics. These models are often used in circuit simulators to represent device characteristics because of the ease of evaluation: the circuit simulator[8] SPICE exclusively uses equivalent circuit models. For semiconductor devices the equivalent circuit model elements are highly nonlinear and element values are strongly dependent on DC bias, frequency, signal level and temperature.

# 3. Choice of the Model

When it comes to simulate any circuit, we need to select a model among various other models available in the library of the circuit or device simulators. Choice of the model should be such that it does not compromises with the accuracy of the system and at the same time it gives efficient result depending on the system or circuit. It also depends over the operating range of interest and the computational efficiency of simulating large circuits. For example, Berkeley SPICE has four different levels of MOSFET models. The combined requirements of computational efficiency and available memory restrict the device models for circuit simulators into the following three categories.

## 1. Analytical Models

There are basically two types of analytical models[9] where model equations are directly derived from device physics. One type of model is based on surface potential analysis called as charge sheet models. In other thype various approximations are done on semiconductor equations to derive the models. These are refered to as semi-empirical analytical model.

## 2. Table Lookup Model

In a table lookup model[10] the device current data are stored for different bias points and device geometries in a tabular form[11]. Generally some sort of interpolation scheme is used to obtain the current values which are not stored.

## 3. Empirical Model.

In an empirical model, the model equations are of the curve fitting type and are thus not based on device physics [12]. The model equations represents the device characteristics. The only advantage of this type of model is that it requires small data storage as compared to table look models and model development time is shorter compared to other modeling approaches. The disadvantage is that this approach is not technology independent.

# 4. Device Modeling using ANFIS

The idea of modeling a transistor based on computational intelligence, is given in [13] which takes Artificial Neural Network (ANN) model implementation[14] into circuit simulator software. Obtaining an accurate model by an ANFIS and implementing the ANFIS model into circuit simulator software such as PSPICE have remained as a challenge.

This paper presents the applicability of an ANFIS for the simulation of the transistor based circuits. The ANFIS could be used to provide a general link from measurements or device simulations to circuit simulation. The data thus obtained can be used as the target data set for optimizing the ANFIS architecture.

In this study, we will create the database for optimizing the ANFIS structure based on data obtained by simulation of transistor on device simulator. After optimization, we will compare the simulation results of the proposed ANFIS model with the device simulator. Finally, the ANFIS model of the transistor can be used as a sub-circuit in the PSPICE software for the modeling and simulation of the other circuits.

# ANFIS

ANFIS is an adaptive network which permits the application of neural network topology together with fuzzy logic. The ANN[15] provides effective learning methods and fast computations, whereas the fuzzy set theory allows thinking and reasoning capability for the fuzzy logic. The learning usually applies to the membership function parameters of the IF-THEN part of the fuzzy rules [16], [17].

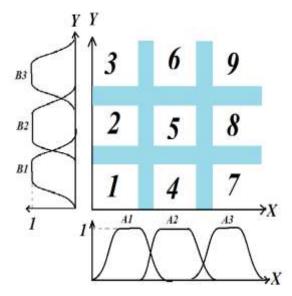

At the computational level, the ANFIS can be regarded as a flexible mathematical structure that can approximate a large class of complex nonlinear systems to the desired degree of accuracy. In the fuzzy section, only the zeroth-order or firstorder Sugeno inference system or the Tsukamoto inference system can be used. For simplicity, we assume that the fuzzy inference system has two inputs (x, y) and one output (f). For a first-order Sugeno fuzzy model, a typical rule set with fuzzybased IF-THEN rules can be expressed as follows:

Rule 1: If x is A1 and y is B1, then

$f_I = p_I x + q_I y + r_I \tag{1}$

Rule 2: If x is A2 and y is B2, then

$$f_2 = p_2 x + q_2 y + r_2 \tag{2}$$

Figure 2. Rule base for ANFIS with three MFs

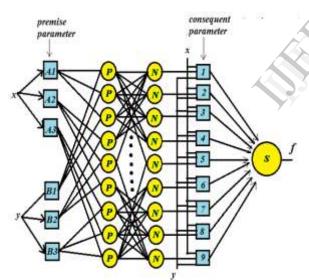

Figure 3. General architecture of ANFIS

Here  $p_i$ ,  $q_i$ , and  $r_i$  are linear output parameters (consequent parameters), where i = 1, 2.

One possible ANFIS architecture to implement these two rules is shown in Fig. 1. It should be noted that the circle indicates a fixed node, whereas the square indicates an adaptive node.

A description of the layers in the network is summarized as follows:

Layer 1: This is a adaptive layer since very node in this layer is adaptive node. It has anode function.

$$O_{1,i} = \mu_{Ai}(x), \qquad i=1,2,...$$

(3)

$$O_{1,i} = \mu_{Bi-2}(y), \quad i=3,4,\dots$$

(4)

where *i* is the membership grade of a fuzzy set  $(A_1, A_2, B_1, B_2)$  and O1, i is the output of the node *i*.

The membership function which is used in this study is the Gaussian bell shaped membership function given by

$$\mu_{A}(x) = \exp\left[\frac{-0.5(x-c^{2})}{a^{2}}\right]$$

where a and c are referred to as premise parameters.

Layer 2: In this layer each node is a fixed node and it calculates the firing strength of a rule using multiplication . The outputs in this layer are given by

#### $O_{2,i} = w_i = \mu_{Ai}(x). \ \mu_{Bi-2}(y)$

Layer 3: Every node in this layer is also fixed and it performs a normalization of the firing strength from the previous layer.

The outputs of this layer are called normalized firing strengths and are given by

$$O_3 = \overline{wi} = \frac{wi}{w1+w2}$$

where O3, i denotes the Layer 3 output.

Layer 4: In this layer, all nodes are adaptive, and the output of a node is the product of the normalized firing strength and a first-order polynomial given by

$$O_{4, i} = \overline{w}_i f = \overline{w}_i (p_i x + q_i y + r_i), \qquad i = 1, 2,$$

where  $\overline{w} i$  is the output of Layer 3, and (pi, qi, ri) is the

parameter set. Parameters in this layer are referred to as the consequent parameters.

Layer 5: The single node in this layer is a fixed node and computes the overall output as the summation of contribution from each rule:

$$O_{5,i} = \sum_i \text{wi fi} = \frac{\sum \text{wi fi}}{\sum \text{wi}}$$

, i=1, 2

where O5, i denotes the Layer 5 output.

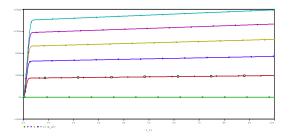

Figure 4. BJT characterstic using PSPICE

|  | Table 1. | Data ranges | for propose | ed anfis model |

|--|----------|-------------|-------------|----------------|

|--|----------|-------------|-------------|----------------|

| Range | IB(uA) | VCE(V) |

|-------|--------|--------|

| Min   | 0      | 0      |

| Max   | 1      | 2      |

In this project ANFIS is used which is a type of neuro-fuzzy[18], [19] modeling. It is used for modeling the character of important parameters of bipolar transistor. The model will be considered with several inputs and one output.

In case of bipolar transistor, the input parameters which is considered is the collectoremitter voltage(Vce) and collector current(Ic). The output parameter which is considered is current of base of bipolar transistor.

## 5. Results and discussion

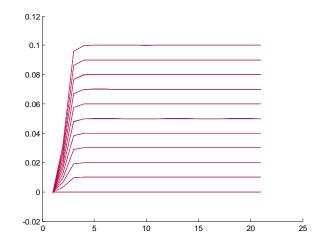

In order to optimize the ANFIS model, about 500 data were obtained by simulation of the BJT by using PSpice. The characteristic of BJT using PSPICE is shown in Fig. 4. The minimum and maximum data ranges for the transistor model is shown in Table. I. About 80% of the data was selected to train the ANFIS model, and the remaining was used to test the performance of the trained ANFIS model. The testing and training were selected randomly from the original database. The improved optimized ANFIS model structure has 24 membership. This optimized model has made it possible to implement the ANFIS model into the circuit simulator software.

The comparison of current characteristics (Ic-Ib and Ib-Vbe) between the PSpice simulation and the proposed ANFIS model for BJT is shown in Fig. 5.

The results show that there is an excellent agreement between the numerical and predicted values with the

Figure 5. Characteristics curve for BJT using PSPICE simulation data and ANFIS model

least errors. Also, we can extend the number of input parameters of the ANFIS model to other parameters.

Besides high accuracy, the calculations speed of the proposed ANFIS model to obtain the results is extremely high.

In this paper, we have proposed the ANFIS model for a BJT. The ANFIS model could significantly reduce the output errors. Another advantage of the ANFIS is the lower number of epochs needed to reach convergence (1,000 in comparison with 10,000). Therefore, the training time for the ANFIS model is definitely less than the required time for designing similar models using pure neural networks. It means that the ANFIS model is better than ANN for redeveloping the model and increasing the input parameters. It may be noted that for an ANN model, we have to perform a trial and error process to develop the optimal network architecture, while the ANFIS model does not require such a procedure. This is because the ANFIS is more transparent, and it is possible to obtain input output relationships from membership functions and IF-THEN rules.

## 6. Conclusion

The general approach of developing a model which matches the behavior of the transistor as specified in the data set, and yields reasonable outcomes for situations not specified in the data set is used. Neuro-fuzzy approach is used for the modeling of BJT in which both the advantages of neural network and fuzzy systems are mixed to get the required behavior of the transistor. For achieving this, the back-propagation algorithm for feed-forward networks, together with the recent work on device modeling and circuit simulation, is merged into a new and probably viable modeling strategy.

#### 7. References

- P. Antognetti, D. O. Pederson, and H. De Man, Eds., *'Computer Design Aids for VLSI Circuits'*, NATO Advanced Institute 1980, Sigthoff & Noordhoff, Alphen aan den Rijn, The Netherlands, 1981.

- [2] L. W. Nagel, 'SPICE2: A computer program to simulate semiconductor circuits', Memorandum No. UCB/ERL-M520, Electronic Res. Lab., University of California, Berkeley, May 1975.

- [3] A. R. Boothroyd, S. W. Tarasewicz, and C. Slaby, 'MISNAN-A physically based continuous MOSFET model for CAD applications', IEEE Trans. Compter-Aided Design, CAD-10, pp. 1512-1529 (1991).

- [4] G. Bischoff and J. P. Krusius, 'Technology independent device modeling for simulation of integrated circuits for FET technologies', IEEE Trans. Computer-Aided Design, CAD-4, pp. 99-1 10 (1985).

- [5] J. A. Barby, J. Vlach, and K. Singhal, 'Polynomial splines for MOSFET model approximation', IEEE Trans. Computer-Aided Design, CAD-7, pp. 557-565 (1988).

- [6] M. R. Pinto, C. S. Rafferty, and R. W. Dutton, 'PISCES-11: Poisson and continuity equation solver', Stanford Electronic Lab. Tech. Rep., Sept. 1984.

- [7] T. Toyabe, H. Masuda, Y. Aoki, H. Shukuri, and T. Hagiwara, 'Three-dimensional device simulator CADDETH with highly convergent matrix solution algorithm', IEEE Trans. Computer-Aided Design, CAD-4, pp. 482-488 (1985).

- [8] R. Beresford and J. Domitrowich, 'Survey of circuit simulators', VLSI Design, Vol. 8, pp. 70-80, July 1987.

- [9] R. F. Vogel, 'Analytical MOSFET model with easily extracted parameters', IEEE Trans. Computer-Aided Design, CAD-4, pp. 127-134 (1985).

- [10] T. Shima 'Table look-up MOSFET capacitance model for short channel devices', IEEE Trans. Computer-Aided Design, CAD-5, pp. 624-632 (1 986).

- [11] J. A. Barby, J. Vlach, and K. Singhal, 'Polynomial splines for MOSFET model approximation', IEEE Trans. Computer-Aided Design, CAD-7, pp. 557-565 (1988).

- [12] P. Antognetti and G. Massobrio, Eds., Semiconductor Device Modeling with SPICE, McGraw-Hill Book Company, New York, 1988.

- [13] M. Hayati, M. Seifi, and A. Rezaei, "The Computational Intelligence in Simulation of DG MOSFET: Application to the Simulation of the Nanoscale COMS Circuit," *ICSE Proc., Johor Bahru*, Malaysia, pp. 138-142,(2008).

- [14] H. Ben Hammouda et al., "Neural-Based Models of Semiconductor Devices for SPICE Simulator," American J. of Applied Sciences, vol. 5, pp.385-391, (2008)

- [15] F. Djeffal et al., "An Approach Based on Neural Computation to Simulate the Nanoscale CMOS Circuits: Application to the Simulation of CMOS Inverter," *Solid-State Electron.*, vol. 51, pp. 48-56, (2007).

- [16] R. Babuska, Fuzzy Modeling for Control, Norwell, MA: Kluwer Academic Publishers, pp. 90-150,(1998).

- [17] T. Takagi and M. Sugeno, "Fuzzy Identification of Systems and Its Applications to Modeling and Control, *IEEE Trans. Syst., Man, Cybern.*," vol. 15, no. 1, pp. 116-132, Feb. 1985.

- [18] J.S.R. Jang, C.T. Sun, and E. Mizutani, *Neuro-Fuzzy and Soft Computing*, New Jersey: Prentice Hall, pp. 510-514,(1997).

- [19] J.S.R. Jang and C.T. Sun, "Neuro-Fuzzy Modeling and Control," Proc. IEEE, p. 378, (1995).