# **Analysis of Single Phase Quasi-Z Source Cascaded Multi Level Inverter**

M. Banupriya<sup>1</sup> <sup>1</sup>Lecturer,

Department of Electrical and Electronics Engineering, Sri Vinayaga Polytechnic College, Krishnagiri Dist. – 635201, Tamil nadu, India.

A. Suvalakshmi<sup>2</sup> <sup>2</sup>Student,

Department of Electrical and Electronics Engineering, Alagappa Chettiar Government College of Engineering and Technology,

Karaikudi – 630004, Tamil Nadu, India.

S. Kalaiarasi<sup>3</sup>, R. Lakshmi<sup>4</sup>, C. Manishka<sup>5</sup> <sup>3, 4, 5</sup>Student.

Department of Electronics and Communication Engineering, Rajagopal Polytechnic College, Gudiyattam - 632 602, Tamil nadu, India

Abstract: -Recently, power electronics converter plays an energetic role in medium and high power applications due to increasing penetration of renewable energy such as solar, wind and demand requirements in terms of efficiency and reliability. Initially conventional inverter converts a dc input voltage to a symmetric ac output voltage of desired magnitude and frequency. The waveform of conventional inverter is nonsinusoidal and contains certain harmonics. To overcome the drawbacks of conventional inverter multilevel inverter has been introduced.

Keywords: Quasi-Z Source, Cascaded Multi Level Inverter

#### 1. INTRODUCTION

Multilevel Inverters (MI) have inherent features such as improved quality of output waveforms, lower total harmonic distortion (THD).smaller filter size, lower electromagnetic interference (EMI), smaller common-mode (CM) voltage and it can operate with a lower switching frequency are gaining more attention for different Basically, three different types applications. topologies in multilevel inverter have been presented such as (i) Diode clamped multilevel inverter (ii) Flying capacitor multilevel inverter (iii) Cascaded H-bridge multi level inverter. However, in diode clamped multilevel inverter, for more than three levels, the charge balance gets disturbed and Output voltage gets limited [1].

In flying capacitor multilevel inverter Clamping capacitors need to be pre charged at a certain voltage and it requires a large number of bulk capacitors. Compared with other topologies, cascaded H-bridge multilevel inverter has some advantages such as it does not require an additional component like diodes and capacitors, more scalable operation voltage sharing between devices is automatic, allows redundancy by using more number of cells per phase, high voltage can be easily achieved and the circuit is completely modular. Based upon the attractive features cascaded multilevel inverter was implemented in various applications. The Quasi Z-Source Inverter also integrated with multilevel inverter to improve the boosting capability. Quasi z source based multilevel inverter topology for DC-DC power conversion has attracted a lot of interest due to its advantages of voltage bucking and boosting capability, high gain when compared to the conventional inverter topologies. At first, conventional voltage source inverter (VSI), ac output voltage is limited to less than the dc input voltage. To overcome this disadvantage, dc-dc boost converter has been additionally added to obtain the required voltage level. Owing to use of this boost converter which is increases the cost and decreases the efficiency of inverter. To avoid this situation QZSCMI is proposed. In this traditional dc link is replaced by impedance network then the dc voltage is boosted through the shoot through state. Therefore, it number of components is reduced and reliability has been improved. The performance of this inverter is also enhanced by Pulse width modulation techniques. Compared with other PWM Techniques Phases Shifted Sinusoidal Pulse Width Modulation, which is produces low total harmonic distortion to get a better sinusoidal output waveform [2]. An integrated inverter topology of quasi-z source H-bridge multilevel inverter; due to its valuable merits; when evaluate with conventional voltage source inverters and zsource inverters.

The implementation of Quasi Z-source cascaded multi level inverter has the objectives of enhancing the properties by using Shoot through duty cycle control method in hardware along with reduced components, shoot through duty cycle with reduced total harmonics distortion [3]. The simulation of proposed circuit has implemented by using MATLAB.

#### 2. OUASI-Z SOURCE INVERTER

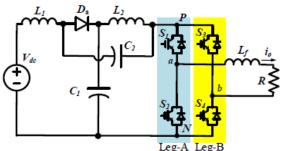

The Quasi-Z Source Inverter circuit differs from that of conventional Z-Source Inverter in LC impedance network interface between the source and inverter. Fig.4.1 shows the basic topology of Quasi Z-source inverter. The advantages make the Quasi Z-source inverter suitable for power conditioning in renewable energy system. The Z-Source Inverter (ZSI) has been reported suitable for residential PV system because of the capability of voltage boost and inversion in a single stage [4]. Recently, four new topologies, the quasi Z-Source Inverter (qZSI), have been derived from the original ZSI. This paper analyzes

ISSN: 2278-0181

**NCFTET - 2020 Conference Proceedings**

one voltage fed topology of these four in detail and applies it to PV power generation systems as shown in below Fig.1

Fig.1 Basic Circuit of Quasi-Z Source Inverter

By using the new quasi Z-source topology, the inverter draws a constant current from the PV array and is capable of handling a wide input voltage range. It also features lower component ratings and reduced source stress compared to the traditional ZSI [5]. It is demonstrated from the theoretical analysis and simulation results that the proposed qZSI can realize voltage buck or boost and dc-ac inversion in a single stage with high reliability and efficiency, which makes it well suited for PV power

#### 3. PROPOSED SYSTEM CIRCUIT ANALYSIS

In the same manner as the traditional ZSI, the qZSI has two types of operational states at the dc side: the non shoot through states (i.e. the six active states and two conventional zero states of the traditional VSI) and the shoot-through state (i.e. both switches in at least one phase conduct simultaneously). In the non-shoot-through states, the inverter bridge viewed from the dc side is equivalent to a current source. The shoot through state is forbidden in the traditional VSI, because it will cause a short circuit of the voltage source and damage the devices. With the qZSI and ZSI, the unique LC and diode network connected to the inverter bridge modify the operation of the circuit, allowing the shoot through state. This network will effectively protect the circuit from damage when the shoot-through occurs and by using the shoot-though state, the quasi Zsource network boosts the dc-link voltage. The major differences between the ZSI and qZSI are the qZSI draws a continuous constant dc current from the source.

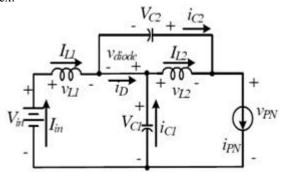

#### 3.1 ACTIVE MODE

In the non-shoot through mode, the switching pattern for the QZSI is similar to that of a VSI. The inverter bridge, viewed from the DC side is equivalent to a current source inverter. The input DC voltage is available as DC link voltage input to the inverter [6], which makes the QZSI behave similar to a VSI shown in Fig.2.

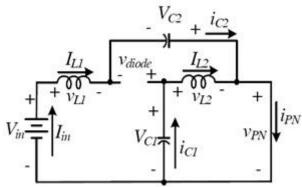

### 3.2 SHOOT THROUGH MODE

In the shoot through mode, switches of the same phase in the inverter bridge are switched on simultaneously for a very short duration [7]. The source however does not get short circuited when attempted to do so because of the presence of LC Network, while boosting the output voltage. The DC link voltage during the shoot through mode, is boosted by a boost factor, whose value depends

on the shoot through duty ratio for a given modulation index.

Fig.2 Equivalent Circuit of the qZSI in Active Mode

Fig. 3 Equivalent Circuit of the qZSI in Shoot-Through Mode

All the voltages as well as the currents are defined in and the polarities are shown with arrows. Assuming that during one switching cycle T, the interval of the shoot through mode is  $T_0$ ; the interval of non-shoot-through states is  $T_1$ ; thus one has  $T = T_0 + T_1$  and the shoot through duty ratio, D = $T_0/T$  from Fig.3. Which is a representation of the inverter during the interval of the non-shoot through states  $T_1$ , one can get,

$$V_{L1}=V_{in}-V_{C1}$$

,  $V_{L2}=-V_{C1}$  (1)

and

$$V_{PN} = V_{C1} - V_{L2} = V_{C1} = V_{C2}V_{diode} = 0$$

(2)

Fig.4.3.which is a representation of the system during the interval of the shoot through states T<sub>0</sub>, one can get;

$$V_{L1} = V_{C2} - V_{in}$$

,  $V_{L2} = V_{C1}$  (3)

$$V_{PN}=0$$

$V_{diode}=V_{C1}=V_{C2}$  (4)

At steady state, the average voltage of the inductors over one switching cycle is zero. From (1), (2), one has

Ing cycle is zero. From (1), (2), one has

$$V_{L1} = V_{L1} = \frac{To(Vc2 + Vin) + T2(Vin - VC2)}{T} = 0$$

$$V_{L2} = V_{L2} = \frac{(Vc2)T0 + (-Vc2)T2}{T} = 0$$

Thus

$$V_{c1} = \frac{T1}{T1 - T0}Vin$$

$$V_{c2} = \frac{To}{T1 - T0}Vin$$

(5)

From (3), (4) and (5), the peak dc-link voltage across the inverter bridge is

$$V_{PN} = V_{CI} + V_{c2} = \frac{T}{T_1 - T_n} Vin = \frac{1}{1 - 2\frac{T_0}{T}} Vin = BVin$$

(6)

ISSN: 2278-0181

Where, B is the boost factor of the qZSI. This is also the peak voltage across the diode. The average current of the inductors  $L_1$ ,  $L_2$  can be calculated by the system power rating P.

$$I_{L1}=I_{L2}=L_{in}=\frac{P}{Vin}$$

(7)

According to Kirchhoff's current law and (4.7), we also can get that

$$I_{c1} = I_{c2} = I_{PN} - I_{L1}$$

$I_{D} = 2I_{LL} - I_{PN}$  (8)

The Voltage and Average current of the qZSI and ZSI Network are shown in Table 1.

The stress on the ZSI is shown as well for comparison, where,

M is the modulation index; is the ac peak phase voltage; P is the system power rating.

$M = T_1 / T_2 - T_0$ ;  $n = T_0 / T_1 - T_0$  thus m > 1; m - n = 1;

$B = T/T_1 - T_0$  thus m+n=B, 1 < m < B

From Table 1 We can find that the qZSI inherits all the advantages of the ZSI. It can buck or boost a voltage with a given boost factor. It is able to handle a shoot through state, and therefore it is more reliable than the traditional VSI. It is unnecessary to add a dead band into control schemes, which reduces the output Distortion.

Table: 1 Voltage and Average Current of the qZSI and ZSI Network

| TACEWOIK |                            |            |                   |           |                    |       |  |

|----------|----------------------------|------------|-------------------|-----------|--------------------|-------|--|

|          | $v_{L1} = v_{L2}$          |            | $v_I$             | PN        | $v_{\it diode}$    |       |  |

|          | $T_0$                      | $T_1$      | $T_0$             | $T_1$     | $T_0$              | $T_1$ |  |

| ZSI      | $mV_{in}$                  | $-nV_{in}$ | 0                 | $BV_{in}$ | $BV_{in}$          | 0     |  |

| qZSI     | $mV_{in}$                  | $-nV_{in}$ | 0                 | $BV_{in}$ | $BV_{in}$          | 0     |  |

|          | $V_{C1}$                   |            | $V_{C2}$          |           | $\hat{v}_{ m ln}$  |       |  |

| ZSI      | $mV_{in}$                  |            | $mV_{in}$         |           | $MBV_{in}$ / 2     |       |  |

| qZSI     | $mV_{in}$                  |            | $nV_{in}$         |           | $MBV_{in}$ / 2     |       |  |

|          | $I_{in} = I_{L1} = I_{L2}$ |            | $I_{C1} = I_{C2}$ |           | $I_D$              |       |  |

| ZSI      | $P/V_{in}$                 |            | $I_{PN}-I_{L1}$   |           | $2I_{L1}-I_{PN}$   |       |  |

| qZSI     | $P/V_{in}$                 |            | $I_{PN}-I_{L1}$   |           | $2I_{L1} - I_{PN}$ |       |  |

In addition, there are some unique merits of the qZSI when compared to the ZSI:

- i. The two capacitors in ZSI sustain the same high voltage; while the voltage on capacitor C<sub>2</sub>in qZSI is lower, which requires lower capacitor rating.

- ii. The ZSI has discontinuous input current in the boost mode; while the input current of the qZSI is Continuous due to the input inductor L<sub>1</sub>, which will significantly reduce input stress.

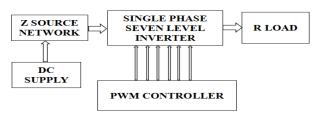

#### 4. BLOCK DIAGRAM OF PROPOSED SYSTEM

In this chapter, from DC supply is given to Z-Source Network, from Z-source network, it is given to single phase seven level inverter, it is then given to R Load. Then from PWM controller is given to single phase seven level inverter to R Load.

Fig. 4 Block diagram of the proposed system

The proposed system uses a cascaded combination single phase quasi Z-source inverter topologies. This topology is used to generate a seven inverter output. Main the main blocks involved in this topology are discussed below. A quasi Z-source network which is connected to a single phase H-bridge this constitutes a single module. A total of three such modules are used to produce the seven level output. The arrangement of this module is in series fashion [8]. A PWM generator is used to produce the desired output from the inverter topology.

## 5. SEVEN LEVEL CASCADED QUASI-Z SOURCE INVERTER

The configuration of the proposed single phase quasi cascaded H-Bridge seven level boost inverter is shows in Fig.5. The proposed inverter consists of three separate DC source, three quasi boost inverter module and capacitor filter connected in resistive load in series [9]. Each module contains five capacitor, three boost inverter, twelve switches, and six diodes. The output voltage of proposed OZSCMI has seven levels

The Shoot though state, the (quasi Z source network boosts the dc-link voltage. Comparing with the normal Z source inverter, the impedance are arranged so as to form the represented structure of qZSI. The proposed Quasi Z source based seven level cascaded inverter is controlled with their AC outputs transiting between the seven distinct voltages. They are: +3Vdc, +2Vdc, +Vdc, 0, -Vdc, -2Vdc,-3Vdc. To obtain the seven levels, the required switching scheme is given in Table.2. The presented qZSI is expected to perform better, since performance limitations commonly associated with dead-time delay which was avoided. The qZSI network is responsible for the voltage boost up. The inversion is performed by supplying PWM signals to the switches of the circuit in a certain fashion so as to produce seven levels at the output. Inductors L1 and L2 have the same values and Capacitors C1 and C2 have the same values. QZSI network is a symmetrical network [10]. The operating states of the qZSI are shoot through zero state and non-shoot through zero state. In this proposed inverter the number of bridges required is 3 hence it consists of 12 switches.

ISSN: 2278-0181

| N | <b>CFTET</b> | - 2020 | Conference | <b>Proceedings</b> |

|---|--------------|--------|------------|--------------------|

|   |              |        |            |                    |

| TD 11 0  | . 1 .     | 1      | C     |       | 1 1   | CATT |

|----------|-----------|--------|-------|-------|-------|------|

| Lable: 2 | switching | scheme | tor s | seven | ievei | CMLL |

|          |           |        |       |       |       |      |

|       |       |                |                |                |                |                  |                  | ۵.               | ٠.               | S <sub>5</sub> | S <sub>6</sub> |               |

|-------|-------|----------------|----------------|----------------|----------------|------------------|------------------|------------------|------------------|----------------|----------------|---------------|

| $S_1$ | $S_2$ | S <sub>3</sub> | S <sub>4</sub> | S <sub>5</sub> | S <sub>6</sub> | S <sub>1</sub> ' | S <sub>2</sub> ' | S <sub>3</sub> ' | S <sub>4</sub> ' | ,              | ,              | Vab           |

| 1     | 0     | 0              | 1              | 1              | 0              | 0                | 1                | 1                | 0                | 0              | 1              | +3<br>Vdc     |

| 1     | 0     | 0              | 1              | 1              | 0              | 0                | 1                | 1                | 0                | 1              | 0              | +2<br>Vdc     |

| 1     | 0     | 0              | 1              | 0              | 1              | 0                | 1                | 1                | 0                | 1              | 0              | +1<br>Vdc     |

| 1     | 0     | 1              | 0              | 0              | 1              | 0                | 1                | 1                | 0                | 1              | 0              | 0             |

| 0     | 1     | 1              | 0              | 0              | 1              | 1                | 0                | 1                | 0                | 0              | 1              | -<br>1V<br>dc |

| 0     | 1     | 1              | 0              | 0              | 1              | 1                | 0                | 0                | 1                | 0              | 1              | 2V<br>dc      |

| 0     | 1     | 1              | 0              | 0              | 1              | 1                | 0                | 0                | 1                | 1              | 0              | 3V<br>dc      |

|       |       |                | (m-            | 1)             |                |                  |                  |                  |                  |                |                |               |

Total harmonic distortion (THD) is a term used to describe the net deviation of nonlinear waveform ideal sine waveform characteristics. Total harmonic distortion is the ratio between the RMS value of the harmonics and the RMS value of the fundamental.

H (n) =  $4/\pi n$  [ cos n $\alpha$ 1 + cos n $\alpha$ 2 +cos n $\alpha$ 3 +...+cos n $\alpha$ s] n=1,3,5,7 etc

The angles  $\alpha 1, \alpha 2, \alpha 3, ..., \alpha s$ , can be chosen such that the voltage total harmonic distortion is a minimum. Generally, these angles are chosen so that predominant lower frequency harmonics, 5th, 7th, 11th, and 13th, harmonics are eliminated.

THD=

$$\frac{\sqrt{\sum_{h=3,57...}^{\infty}Vh2}}{V_1} \times 100\%$$

(10)

where: m= Number of levels

#### 6. SIMULATION RESULTS ANALYSIS

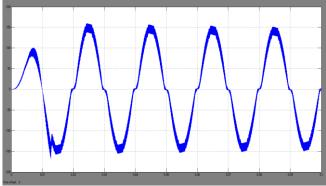

In the chapter simulation result of the proposed system and the corresponding voltage waveforms are obtained. The simulation has been done using MATLAB/SIMULINK. Fig.5 shows the seven level output voltage waveform of the proposed system with amplitude 150V.

Fig.5 Seven level output voltage waveform

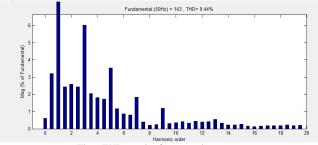

Fig.6 THD result of proposed system

In this project the comparison of THD for single Phase cascaded H bridge multilevel inverter is done between 5level and 7- level. Single phase cascaded H Bridge inverters are implemented in MATLAB/SIMULINK. A MOSFET is selected as a switch. The switches are triggered at regular intervals.

Table: 3 THD comparisons

| S.no | No .of levels | THD   |

|------|---------------|-------|

| 1    | 5             | 18.82 |

| 2    | 7             | 09.44 |

#### 7. CONCLUSION

The performance of the Quasi Z-Source cascaded H bridge multilevel inverter has been investigated based on its THD evaluation in this project work. The single phase seven level QZSCMI was estimated through the FFT analysis. Simulations have been developed in Matlab/Simulink for seven level Quasi Z-source cascaded multilevel inverter with R load. Input voltage across each bridge is taken to be 12V and the output obtained is 24V.By using PSSPWM, THD is reduced and measured to be 10.31% which has been lower than conventional inverter THD value. The QZSCMI boost a voltage and it also operates in shoot through state. The results confirmed that the proposed system is more reliable and cost effective than the conventional multilevel inverter, which reduces the output distortion and produces a better output waveform. The hardware results also confirm the superiority of the proposed QZSCMI.

#### 8. REFERENCES

- [1] S. Kouro, et al, "Recent advances and industrial applications of multilevel converters," IEEE Trans. Ind. Electron., vol. 57, no. 8, pp. 2553–2580, Aug. 2010.

- [2] M. Malinowski, K. Gopakumar, J. Rodriguez, and M. A. Perez, "A survey on cascaded multilevel inverters," IEEE Trans. Ind. Electron., vol. 57, no. 7, pp. 2197–2206, July 2010

- [3] G. Farivar, B. Hredzak, and V. G. Agelidis, "A DC-side sensor less cascaded H-bridge multilevel converter-based photovoltaic system," IEEE Trans. Ind. Electron., vol. 63, no. 7, pp. 4233–4241, July 2016.

- [4] J. Chavarría, D. Biel, F. Guinjoan, C. Meza, and J. J. Negroni, "Energy-balance control of PV cascaded multilevel grid-connected inverters under level-shifted and phase-shifted PWMs," IEEE Trans. Ind. Electron., vol. 60, no. 1, pp. 98–111, Jan. 2013.

- [5] M. Coppola, F. D. Napoli, P. Guerriero, D. Iannuzzi, S. Daliento, and A. D. Pizzo, "An FPGA-based advanced control strategy of a grid-tied PV CHB inverter," IEEE Trans. Power Electron, vol. 31, no. 1, pp. 806–816, Jan. 2016.

- [6] Villanueva, P. Correa, J. Rodríguez, and M. Pacas, "Control of a single-phase cascaded H-bridge multilevel inverter for grid-connected photovoltaic systems," IEEE Trans. Ind. Electron., vol. 56, no. 11, pp. 4399–4406, Nov. 2009.

- [7] Farivar, C. D. Townsend, B. Hredzak, J. Pou, and V. G. Agelidis, "Low-capacitance cascaded H-bridge multilevel StatCom," IEEE Trans. Power Electron, vol. 32, no. 3, pp. 1744–1754, Mar. 2016.

- [8] Khoucha, S. M. Lagoun, K. Marouani, A. Kheloui, and M. E. H. Benbouzid, "Hybrid cascaded H-bridge multilevel-inverter induction-motor-drive direct torque control for automotive applications," IEEE Trans. Ind. Electron., vol. 57, no. 3, pp. 892–899, Mar. 2010.

- [9] S. Vazquez, J. I. Leon, J. M. Carrasco, L. G. Franquelo, E. Galvan, M. Reyes, J. A. Sanchez, and E. Dominguez, "Analysis of the power balance in the cells of a multilevel cascaded H-bridge converter," IEEE Trans. Ind. Electron., vol. 57, no. 7, pp. 2287–2296, Jul. 2010.

- [10] J. Napoles, A. J. Watson, J. J. Padilla, J. I. Leon, L. G. Franquelo, P. W. Wheeler, and M. A. Aguirre, "Selective harmonic mitigation technique for cascaded H-bridge converters with non equal DC link voltages," IEEE Trans. Ind. Electron., vol. 60, no. 5, pp. 1963–1971, May 2013.