# **Current Mode Sense Amplifier for SRAM Memory**

Presented by Ravi Dutt M-Tech Electronics and Comm. M.M. Engineering College Maharishi Markandeshwar University Mullana (Ambala) India ravi2000dutt@gmail.com

Under the guidance of Mr. Abhijeet Lect.in Electronics and Comm. M.M. Engineering College Maharishi Markandeshwar University Mullana (Ambala) India

## Abstract

The sense amplifier is one of the most important components of semiconductor memories used to sense stored date. This plays an important role to reduce the overall sensing delay and voltage. Earlier voltage mode sense amplifiers are used to sense the date it sense the voltage difference at bit and bitb lines but as the memory size increase the bit line and date line capacitances increases. As a result large time is required by capacitance to discharge so sensing delay and power dissipation increase. Used that sense the current directly from bit and bitb lines and reduce the sensing delay. This technique is used in current mode sense amplifiers. This paper explores the design and analysis of current mode sense amplifier using Tanner tool (14.0) version. The simulation is carried out at 1.5V / 0.13um technology using tanner (14.0 Version) tool. The results are verified with the existing results at 1.8V / 0.18um CMOS technology.

## 1. Introduction

Sense Amplifier is the most critical circuit in the periphery of CMOS memory. The performance of SA's strongly affects both memory access time, and overall memory dissipation. As with other ICs today, CMOS memories are required to increase speed, improve capacity and maintain low power dissipation. These objectives are somewhat conflicting when it comes to sense amplifier in memories. This increased bit-line capacitance in turn shows down voltage sensing and makes bit-line capacitance swings energy expensive resulting in slower more energy hungry memories. Due to their great importance in memory performance sense or detect stored data from a read-selected memory cell Sense amplifiers are used to translate small differential voltage to a full logic signal that can be further used by digital logic. The need for increased memory capacity, higher speed, and lower power consumption has defined a new operating environment for future sense amplifiers [6].

Moore's law was the breakthrough and evolution in the semiconductor industry. Moore's law gave the idea to integrate large memory blocks with logic circuits on a single chip but the on-chip memory limits the speed and performance of the overall system. The limiting factor is the increasing bit line capacitance, which results in increased time to develop bit line differential voltage and increase in the delay. For fast and power efficient memory design, both time and signal swing on the bit lines needs to be minimized. [4]

Sense amplifiers are one of the most critical circuits in the periphery of CMOS memories. Their performance strongly affects both memory access time, and overall memory power dissipation. As with other ICs today, CMOS memories are required to increase speed, improve capacity and maintain low power dissipation. These objectives are somewhat conflicting when it comes to design the sense amplifier in memories. With increased memory capacity usually the bit-line parasitic capacitances get increased. This increased bit-line capacitance slows down voltage sensing and these results in slow and more power consuming memories.

Sense amplifiers are mainly used to read the contents of SRAM and DRAM cells. They are very sensitive to noise and their design implies that they will provide adequate noise margins and provide good quality of data that represent the contents of a particular memory cell. There are two categories of sense amplifiers. The static sense amplifiers mainly used to detect logic in the static RAMs and the dynamic sense amplifiers mainly used to save energy when low power dissipation is required. [9]

Fast sense amplifiers are important for achieving low latency in many circuits and the most common domain being bit-line reading in memories. With the advent of sub-micron CMOS chips, interconnection is becoming a major source of on-chip delay, and fast sense amplifiers are also likely to be needed, e.g. as repeaters for highspeed signals which must traverse large chips.

www.ijert.org

1

Sense amplifier can be operated in voltage, current and charge mode but we operate them in current-mode because they present a low impedance to the inputs and respond to the differential current rather than to the voltage between the inputs, this can reduce interconnect delay in long wires there by providing speed improvement. The current mode sense amplifier reduces and the low output resistance of the short-channel transistors

motivation to use current mode sensing in the bit lines in SRAM. [5]

The speed of the sensing operation depends on the ability of the sense amplifier as to how fast it can resolve or decide that which of the two bit lines current is higher in magnitude and accordingly provide a logic value of "1" or "0" in the output.

# 2. Current mode sense-amplifier circuit

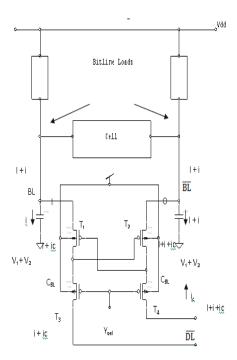

The sense amplifier is selected by grounding the Ysel node as shown in fig-1. Then the currents will flow through the transistors via the bit-line loads. The drains of T3 and T4 are connected to data lines, which are close to ground level. This means that these transistors operate in saturation. The bit-line loads are low ohmic to ensure that the bit lines are always close to VDD during read access.

Figure-1 Current mode sense amplifier [1]

The sensing delay is unaffected by the bit-line capacitance since no differential capacitor discharging is required to sense the cell data.

The bit line swing during read operation as compared to voltage mode sensing technique. It proves that current

sensing technique would be faster than voltage mode due to the low impedance termination of the current mode. It shows that current sensing relatively insensitive to the bit line capacitance.

The circuit operates as follows:-Suppose the cell is accessed and draws current I. The gate-source voltage of T1 will be equal to that of T3, since their currents are equal, their sizes are equal, and both transistors are in saturation. This voltage is represented by V1. The same applies to T2 and T4. Their gate-source voltages are represented by V2. It follows that, since Ysel is grounded, the left bit line will have voltage V1 + V2, and the right bit line will also have voltage V1 + V2. Therefore the potential of the bit lines will be equal independent of the current distribution. This means that there exists a virtual short circuit across the bit lines. Since the bit line voltages are equal, the bit-line load current will also be equal, as well as the bit-line capacitor currents. As the cell draws current Icell, it follows that the right-hand leg of the sense amplifier must pass more current than the left-hand leg. In fact, the difference between these currents is Icell (the cell current). The drain currents of T3 and T4 are passed to current transporting data lines DLs.

Sufficient margin from unwanted latching behavior is provided by the bit-line load resistance, the body effect, the differential data-line current is therefore equal to the cell current. Thus we obtain current sensing. The crosscoupled structure is actually a flip-flop configuration, but

A second speed-enhancing feature is provided by the common-mode discharge current pulses from the bit-line capacitors, effectively precharging the sense amplifier (in particular pre charging nodes A and B, and the data lines) as soon as Ysel is grounded. This is a kind of dynamic biasing which is very favourable for speed, and which does not increase the current consumption. Finally, since the bit-line voltages are kept equal, the sense amplifier possesses intrinsic equalizing action. This eliminates the need for bit-line equalization during a read access [1].

The analysis for conventional current mode Sense amplifier is done at TMSC 0.13um technology node with 1.5V power supply. The value of sensing delay is calculated for combinations of CBL = 1PF.

2 www.ijert.org

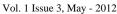

Figure-2 Voltage waveforms of current mode sense amplifier

Voltage Signal of Current Mode Sense Amplifier Circuit at Node-VS

Voltage Signal of Current Mode Sense Amplifier Circuit at Node-CLK

Voltage Signal of Current Mode Sense Amplifier Circuit at Node-WL

Voltage Signal of Current Mode Sense Amplifier Circuit at Node-Out

Voltage Signal of Current Mode Sense Amplifier Circuit at Node-CS

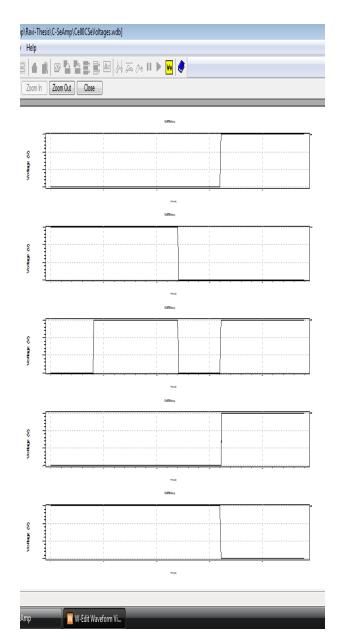

Figure-3 Simulation waveforms of conventional current mode sense amplifier circuit

Table-1 Comparison of sensing delay for current mode sense amplifier at CDL = 1PF, Cout = 0.1 PF and CBL varies from 1 Pf of 5 Pf

| Bit Line<br>Capacitance<br>CBL(pf) | Sensing Delay(ns)                                                      |

|------------------------------------|------------------------------------------------------------------------|

| 1                                  | Measurement result summary - a=1e-012                                  |

| 2                                  | Delay time = 8.3632e-010<br>Measurement result summary -<br>a=2e-012   |

| 3                                  | D delay time = 8.4438e-010<br>Measurement result summary -<br>a=3e-012 |

| 4                                  | Delay time = 8.3396e-010<br>Measurement result summary -<br>a=4e-012   |

| 5                                  | Delay time = 8.2980e-010<br>Measurement result summary -<br>a=5e-012   |

|                                    | Delay time = 8.2191e-010                                               |

3 www.ijert.org

The analysis for conventional current mode Sense amplifier is done at TMSC 0.13um technology node with 1.5V power supply. The value of sensing delay is calculated for combinations of CBL = 1PF,

CDL = 1PF Cout = 0.1Pf as shown in table-1.The analysisshows that the sensing speed of conventional current mode Sense amplifier independent of the variations in bit line capacitances.

### 3. Conclusion

The analysis for Conventional Current mode Sense amplifier is done at TMSC 0.13um technology node with 1.5V power supply. The value of sensing delay is calculated for combinations of CBL = 1PF, CDL = 1PF Cout = 0.1Pf as shown in table-1.

The analysis shows that the sensing speed of Current mode Sense amplifier independent of the variations in bit line capacitances.

### REFERENCES

- [1] E. Seevinck, P.J.V. Beers and H. Ontrop, Current mode techniques for high-speed VLSI circuits with application to current sense amplifier for CMOS SRAM's, IEEE J. Solid-State Circuits 26 (1991) 525-536.

- [2] Anh-Tuan Do, Jeremy Low Yung Shern, Zhi-Hui Kong and Joshua Low Yung Lih, "A Full Current-mode Sense Amplifier for Low-power SRAM Applications" 978-1-4244-2342-2/08/ 2008 IEEE. 1402.

- [3] Adam Makosiej, Piotr Nasal ski, Bastien Giraud, Andrei Vladimirescu, and and Amara Amara, "An Innovative sub-32nm

- SRAM Current Sense Amplifier in Double-Gate CMOS Insensitive to Process Variations and Transistor Mismatch" IEEE International Conference on Electro/Information Technology, 978-1-4244-1811-4 IEEE-2008.

- [4] Abhijit Sil, Eswar Prasad Kolli, Soumik Ghosh and Magdy Bayoumi, "High Speed Single-Ended Pseudo Differential Current Sense Amplifier for SRAM Cell" IEEE International Conference on Electro/Information Technology, 978-1-4244-1684-4 IEEE-2008.

- [5] Do Anh-Tuan, Kong Zhi-Hui, and Yeo Kiat-Seng, "Hybridmode sram sense amplifiers: New approach on transistor sizing", IEEE transactions on circuits and systems, vol. 55, no

- [6] YeoKiat Seng, Goh Wang Ling, Lim Hoe Gee and Zhang Wenle, "New Conditional Sampling Sense-Amplifier-Based Flip-Flop for High-Performance and Low-Power Application" 1-4244-0797-4- 2007 IEEE

- [7] Olivier Thomas, Andrei Vladimirescu and Asmara Amara,"Ultra-Low-Voltage Current-Sense Read Circuits for CMOS SOI SRAM's Olivier Thomas, Andrei Vladimirescu, and and AmaraAmara"2005 IEEE International SOI Conference, 0-7803-9212-4 2005 IEEE

- [8] Zhi-Hui Kong, Kiat Seng Yeo, and Chip-Hong Chang, "An ultra low power current mode sense amplifier for SRAM applications", IEEE Journal of Circuits, Syst., and Comp. 14, (2005) 939-951.

- [9] B.Witch, "Current sense amplifier for embedded SRAM in high performance system on chip", Springer, verlag-berlin heideberg, 2003.

4 www.ijert.org