# Low Noise Amplifier for 1-10GHz Application

Manoj Mishra<sup>[1]</sup> Assistant Professor (EXTC) Atharva College Of Engg. Atharva College Of Engg Mumbai,India

Barnana Dutta<sup>[2]</sup> Assistant Professor (EXTC) Mumbai,India

Shilpa Jaiswal<sup>[3]</sup> Assistant Professor (EXTC) Assistant Professor(EXTC) Atharva College of Engg Mumbai,India

Sweta Jha<sup>[4]</sup> Atharva College of Engg Mumbai,India

Divya Sharma<sup>[5]</sup> Assistant Professor (EXTC) Atharva College Of Engg Mumbai,India

Abstract: In this paper low power consumption amplifier is presented. Signal amplification is one of the most basic & important circuit functions in modern RF & Microwave systems. Initially microwave amplifiers are made up of tubes, such as Klystron & Travelling wave tubes, or solid state reflection amplifiers based on the negative resistance characteristics of Tunnel or Varactor diodes. However due to the dramatic improvements & innovations in solid state technologies that have occurred since the 1970's most RF & microwave amplifiers today use transistor devices such as Si BJT, GaAs, Si MOSFET, GaAs MESFET or GaAS GaN HEMT's. Low power consumption amplifier is versatile demanded in modern technology, modern technology want such type of amplifier which gives low power consumption with less reflection, in this paper presented series and shunt feedback topology with pole zero compensation method for designing of low power consumption amplifier, the primary characteristics of LNA is its noise figure, generally we put a filter circuit before the amplifier for the protection of the amplifier. The scaling of the components increase, increase its number, the similar area of an chip decreases its subthreshold voltage with its increase in the leakage power consumption.. The Power consumption is based on the number of elements and routing of components and its process fabrication. In this paper we are going to developed method to reduce leakage power consumption with reduction of reflection.

## Keywords - Power dissipation; feedback topology; Transistor;pole-zero Compensation technique

## I. INTRODUCTION

The low noise amplifier is used to form the input stage at the receiving part for the communication systems. The main objectives of the sub circuits are to amplify only wanted signals without affecting the signal to noise. When we are going to design microwave low noise amplifier then stability is one of the most important considerations. There are two methods to check the stability, theoretically & graphically. For graphical method we use Smith chart to plot the stability circles, then after the stability we determine the transistors & check the stability of the transistor. After determining the stability of the transistors locate the stable regions on the Smith Chart & then the next step is to design the matching sections.GaAS MOSFETs have a generally low AC input impedance, making them difficult to impedance match, so an external series resistance can be added to the gate to overcome these difficulty, but using this technique noise power of the

amplifiers are increases & efficiency decreases. This drawback can be overcome by adding a series inductor at the source of a MOSFET & this will also reduce the input voltage .This scaling leads decrement in threshold voltage of the circuit and exponential rise in its leakage power [3]. Reduced gate lengths result in an consumption increase in the leakage power dissipation. Increased transistor densities result in an increase in the power dissipation per unit area thereby creating hotspots. Now we continuously scaled down the threshold voltage for increasing the leakage power dissipation. In medical field low noise amplifiers can also be used for patients monitoring & also used in RF Identification. For wireless sensor networks, ultra-low dc-power consumption is a key design issue because of the limited capacity of the smallsize battery power source [10]– [13]. There are so many low noise amplifiers are available, by using the different amplifiers we can achieve a very low power consumption devices. To reduce the power dissipation of the order of mW we use a reflection type amplifiers this topology's unique power-efficient amplification principle with a gain characteristic, which is achieved almost indepen-dently of the bias current, enables utilization of NDR-based microwave amplifiers in ultra-low-power applications [5

#### II. PROPOSED BROAD-BAND LNA DESIGN

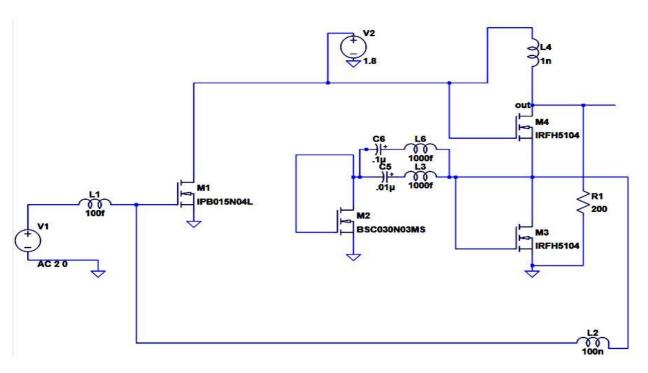

Now we are going to describe the proposed idea of the low noise amplifier. Fig. 1 shows the schematic of the proposed broadband LNA. Our objective is to design an amplifier of 1GHz to 10.The first stage of the following fig. of the amplifier; in second stage we use double pole compensation technique. The value of all elements find out by resonance theory, to reduce the noise figure induced feedback inductor, high mobility NMOS transistor used for design amplifier. The optimal value of 1.8 V for better linearity, the optimization of the proposed work is carried out with the consideration of gain, bandwidth and noise figure. Our objective is to design an amplifier which has constant gain & better matching for the desired frequency range. One of the best examples of constant gain is the conjugate matching. We use the buffer circuit for the input output compensation. To eliminate the output parasitic capacitance in the last stage we add inductor & resistor in series. The series inductor is sized to 100fH so that its parasitic capacitance due to the output stage would not cause reflection degradation at tens of GHz range. As shown in Fig. 2, the simulated power dissipation is between 1-10 GHz which exhibits over 10GHz bandwidth improvement.

Figure I

#### **III. MEASUREMENT RESULTS**

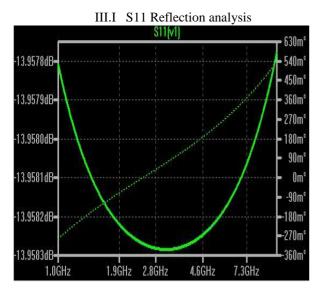

We generally use the LT-spice for the proposed circuit. The proposed LNA achieves a S11 $\leq$  - 13.9dB, between 1-10GHz.

Figure II Measurement Analysis

Figure 4 shows the diagram of measured noise figure which is from 0.4 to 0.8 dB. Due to the presence of the capacitor in the matching section gain decreases. Table I compares the proposed work with other reported state-of-art Broadband LNAs design using nano-scale CMOS technology process [4]–[8]. where are the minimum noise

#### **III.II POWER DISSIPATION ANALYSIS**

figure and minimum power dissipation over the broad bandwidth from 1-10GHz, The proposed work shows excellent performance in terms of its large bandwidth, acceptable I/O return losses verified by S11 Parameters and very less power consumption.

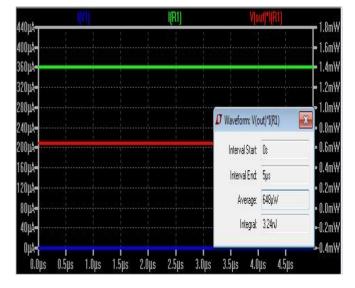

Figure III Power Dissipation analyses

Power dissipation shown in figure 3 this low noise amplifier exist power consumption up to 648uW, power consumption of proposed amplifier is control by using appropriate gate charge and on resistance of transistor, power consumption also control by using reflection elimination method.

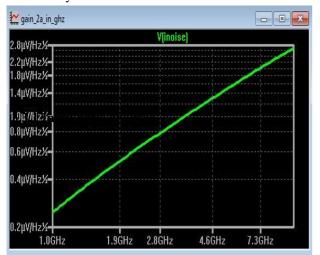

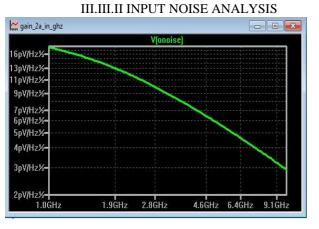

### **III.III NOISE ANALYSIS**

As we described earlier that noise analysis is one of the important considerations, the following figure shows the noise analysis.

Figure IV Input Noise Analysis

Figure 5 Output noise analysis

The figure 5 shows the graphical view of output low noise amplifiers

*Noise Figure*= 10log

Obtain Noise Figure up to .4 to .8dB

Power dissipation shown in Fig. 3. Achieve Power consumption up 648uW, Validation of work is shown in Table-I, simulation done from 1-10GHz.

Table I Comparison of Proposed Work with Literatures

| Ref          | Freq<br>(GHz) | NFmin<br>(dB) | S11<br>(dB) | Power<br>Dissipation<br>(mW) |

|--------------|---------------|---------------|-------------|------------------------------|

| [7]          | 35-44         | 4.6           | ≤-7         | 15                           |

| [8]          | 17.5-26       | 3.3           | ≤-6         | 5.6                          |

| [9]          | 2.1-39        | 4.5           | ≤-8         | 25.5                         |

| This<br>Work | 1-10          | .4 to .8      | ≤-13.9      | 648uW                        |

## IV. CONCLUSION

A 1-10 GHz broadband LNA with a power consumption of 648uW. LT-Spice simulator used for designing and validation of proposed amplifier. A series inductor, feedback inductive technique and double pole zero compensation technique is used to achieve excellent input and out matching over a large bandwidth. In output stage buffer and inductive load is used to eliminate reflection and to provide isolation between input and output stage, this stage also exist low power consumption. a minimum 0.4 to 0.8 dB NF and a S11≤-13.9dB, are achieved from 1GHz to 10GHz. The proposed amplifier presents a broad bandwidth.

#### **IV. REFERENCES**

- C. Pavageau, M. S. Moussa, J.-P. Raskin, D. Vanhoenaker-Janvier, [1] N. Fel, J. Russat, L. Picheta, and

- F. Danneville, "A 7 dB 43 GHz CMOS distributed amplifier on [2] high-resistivity SOI substrates," IEEE Trans. Microw. Theory Tech., vol. 56, no. 3, pp. 587–598, Mar. 2008. S. Chen, J. Kuo, C. Lin, M. Tai, and H. Wang, "A DC- 11.5 GHz

- [3] low-power, wideband amplifier using splitting- load inductive peaking technique," IEEE Microw.

- Ì5]

- Wireless Compon. Lett., vol. 18, no. 7, pp. 482–484, Jul. 2008. P. Chang and S. Hsu, "A compact 0.1–14 GHz ultra-wideband lownoise amplifier in 0.13 m CMOS," IEEE

- [6] Trans. Microw. Theory Tech., vol. 58, no. 10, pp. 2575-2581, Oct. 2010. [7]

- M. Chen and J. Lin, "A 0.1–20 GHz low-power self- biased resistivefeedback LNA in 90 nm digital CMOS,"

- IEEE Microw. Wireless Compon. Lett., vol. 19, no. 5, pp. 323-[8] 325, May 2009.

- M. Okushima, J. Borremans, D. Linten, and G. Goeseneken, "A [9] DC-to 22 GHz 8.4 mW compact dual-feedback wideband LNA in 90 nm digital CMOS," in Proc. IEEE RFIC Symp., Jun. 2009, pp. 295-298

- [10] H.-K. Chen, Y.-S. Lin, and S.-S. Liu, "Analysis and design of a 1.6–28 GHz compact wideband LNA in 90 nm CMOS using a match input network," IEEE Trans.

- [11] Microw. Theory Tech., vol. 58, no. 8, pp. 2092–2014, Aug. 2010.

[12] H.-C. Yeh, Z.-Y. Liao, and H. Wang, "Analysis and design of millimeter-wave low-power CMOS LNA with transformer-multicascode topology," IEEE Trans.

- [13] M.-H. Tasi, S. S. H. Hsu, F.-L. Hsueh, C.-P. Jou, and T.-J. Yeh, "A 17.5-26 GHz low-noise amplifier with over 8 kV ESD protection in 65 nm CMOS," IEEE

- Microw. Wireless Compon. Lett., vol. 18, no. 7, pp. 483-485, Sep. [14] 2012.

- [15] Chen Feng, Xiao Peng Yu, et.al. "A Compact 2.1–39 GHz Self-Biased Low-Noise Amplifier in 65 nm CMOS

[16] Technology" IEEE MICROWAVE AND WIRELESS

- [17] COMPONENTS LETTERS, VOL. 23, NO. 12, DECEMBER 2013 pp 1531-130

[18] D. Wu, R. Huang, W. Wong, and Y. Wang, "A 0.4-V low noise

- ampli-fier using forward body bias technology for 5 GHz application,"IEEE Microw. Wireless Compon.

- [19] Lett., vol. 17, no. 7, pp. 543–545, Jul. 2007.

- [19] Dett., Vol. 17, BD, 7, 99, 545, 547, 507, 2007.

[20] D. Linten, L. Aspernyr, W. Jearnsaksiri, J. Rarnos, A. Mercha, S. Jenei, S. Thijs, R. Garcia, H. Jacobsson, P. Wambacq, S. Donnay, and S. De-coutere, "Low-power 5

- [21] GHz LNA and VCO in 90 nm RF CMOS," in IEEE

- [22] Symp. VLSI Circuits Tech. Dig., 2004, pp. 372-375.

- [23] .Chang,J.Chen,andY.Wang,"Afully-integrated5GHz low-voltage LNA using forward body bias technology,"IEEE Microw. Wireless Compon. Lett., vol.

- [24] 19, no. 3, pp. 176–178, Jul. 2009.

[25] M. Hines, "High-freque ncy negative-resistance circuit principles for esaki diode applications,"Bell Syst. Tech. vol. 39, pp. 477–514, May 1960.