# Phase Locked Loop Design and Implementation using Current Starved Voltage Controlled Oscillator

Neha Pathak M Tech Scholar, Dept of ETC SRIT Jabalpur (M.P), India Prof. Ravi Mohan HOD M tech Dept of ETC SRIT Jabalpur (M.P), India

Abstract— This paper is based on CMOS Current Starved Voltage controlled oscillator (CSVCO) for a Phase Locked Loop (PLL) in 180 nm process and describes the design and implementation of miscellaneous blocks of Phase Locked Loop (PLL) for the 6 GHz band. The reference frequency is 50 MHz and the Current Starved Voltage controlled oscillator output frequency is 1 GHz to 3 GHz in a state-of the-art 180nm process, with 1 V supply voltage. The design is implemented in Zeni Electronic Design Automation (EDA) environment tool with high oscillation frequency and low power consumption. Phase locked loop's were used in most of the application for clock generation and recovery as well. As the technology grows faster in the existing generation, there has to be quick development with the technique.

Keywords- Architecture of PLL, CSVO, microprocessor, ZENI EDA software

### I. INTRODUCTION

A PLL is a feedback system that compares the output frequency/phase with the input frequency/phase. Phaselocked loops can be utilized for frequency synthesizing, carrier synchronization, carrier recovery, frequency division, frequency multiplication and frequency demodulation [1]. A PLL is generally used in wireless communications and data recovery circuits. A VCO is the heart of the PLL and can be designed either by LC or RC. A LC VCOs have superior phase noise performance compared with ring VCO'S. However, an LC VCO has a small tuning range large layout area and possibly higher power [2]. The ring oscillators, however, do not have the complication of the on-chip inductors required for the LC oscillators. Thus the chip area is reduced. In addition to a wide tuning range; ring oscillators with even number of delay cells can produce quadrature phase outputs. The phase noise performance of ring oscillators is much poorer in general [1], [3], [4]. Also, at high oscillation frequencies, the power consumption of the ring oscillators may not be low which is a key requirement for battery operated devices [5]. To overcome these problems, we work on five stages current starved Oscillator and single stage source coupled oscillator without an LC tank. Finally their performances are compared based on their results.

A challenging work in the CMOS technology is to design a low phase noise ring oscillator for a Charge Pump Phase Locked Loop (CPPLL) using CMOS technology. A design presented here is to improve the overall characteristics of PLL. The first component of the PLL is the PFD which has been designed to improve the speed by minimizing the dead zone [16]. The CP circuit improves the performance of the PLL because it has been designed for high bandwidth. The main

part of this PLL is the CSVCO, which has been designed to get superior phase noise.

### II. SYSTEM OVERVIEW

Phase-locked loops (PLLs) generate well-timed on-chip clocks for various applications such as clock and data recovery, microprocessor clock generation and frequency synthesizer. The basic concept of phase locking has remained the same since its invention in the 1930s [1]. However, design and implementation of PLLs continue to be challenging as design requirements of a PLL such as clock timing uncertainty, power consumption and area become more stringent.

This section briefly discusses the basic concept of phase locking. A PLL is a closed-loop feedback system that sets fixed phase relationship between its output clock phase and the phase of a reference clock. A PLL tracks the phase changes that are within the bandwidth of the PLL.

A PLL also multiplies a low-frequency reference clock, to produce a high-frequency clock. A PLL is a negative feedback control system circuit. As the name implies, the purpose of a PLL is to generate a signal in which the phase is the same as the phase of a reference signal. This is done after many iterations of comparing the reference and feedback signals. The overall goal of the PLL is to match the reference and feedback signals in phase, this is the lock mode. After this, the PLL continues to compare the two signals but since they are in lock mode, the PLL output is constant [12].

A basic form of a PLL consists of five main blocks:

- 1. Phase Frequency Detector (PFD)

- 2. Charge Pump (CP)

- 3. Low Pass Filter (LPF)

- 4. Voltage Controlled Oscillator (VCO)

- 5. Frequency divider

# III. PLL ARCHITECTURE

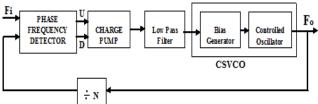

To synchronize the frequency, various types of PLLs are being used in the application of wireless communication. PLLs are consists of PFD, CP, LPF, CSVCO and divider which is shown in Fig. 1. In addition

with CSVCO, the PFD compares feedback signal with input signal and generates the error signal. A charge pump circuit along with LPF is used to minimize the disturbances at the input of CSVCO and to get a sharper and smooth signal at the CSVCO output. To form a phase-locked loop (PLL), the phase error output of PFD is fed to a charge pump and then to loop filter which integrates the signal to get a sharper and smooth signal so that the disturbances at the input of CSVCO get minimized.

Figure (1): Architecture of PLL

# IV. Current-Starved Voltage Controlled Oscillator

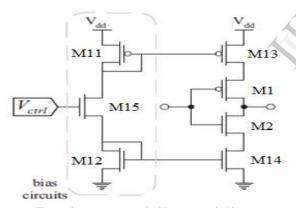

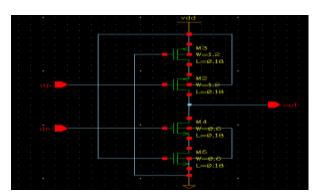

The operation of current starved VCO is similar to the ring oscillator. Figure (2) shows a one stage Current-Starved VCO [2]. Middle PMOSM1 and NMOSM2 operate as inverter, while upper PMOSM11 and lower NMOSM14 operate as current sources. The current sources limit the current available to the inverter. In other words, the inverter is starved for current. The current in the first NMOS and PMOS are mirrored in each inverter/current source stage. PMOSM11 and NMOSM11 drain currents are the same and are set by the input control voltage [2].

Figure (2): current starved with output-switching

The current-starved VCO is as shown in Figure (2) With the current-starved structure, the supply noise would contaminate the output phase. Referring to (6), the output frequency can be assumed to be in terms of the RC delay and n denoting the number of the inverter stages.  $C_{tot}$  denotes the total parasitic capacitance including wire parasitic capacitor ( $C_{wire}$ ), and drain-to-bulk capacitor ( $C_{DB}$ ). For simplifying the analysis,  $C_{DB}$  is assumed to be a constant regardless of the operation mode of the transistors. Moreover, the resistance of the channel of each stage (R) could be estimated as the reciprocal of the transconductance of the MOS. With  $\emptyset_0 = \frac{df_0}{dt}$  the supply noise would change the  $V_{GS}$  of the PMOS and further affect the output frequency and output phase:

$$f_0 \quad \alpha \quad \frac{1}{n. R. C_{tot}}$$

$$= \frac{g_m}{n. C_{tot}}$$

$$= \frac{\mu C_{ox}(\frac{W}{L})(V_{GS} - V_{TH})}{n. C_{tot}}$$

where  $V_{TH}$  denotes the threshold voltage [11].

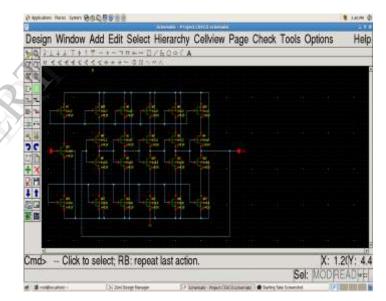

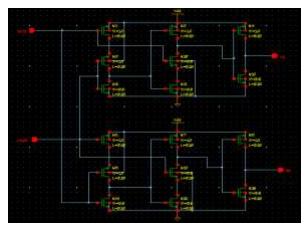

This VCO is designed using ring oscillator and its operation is also similar to that. From the schematic circuit shown in the Figure (3), it is observed that MOSFETs M2 and M3 operate as an inverter, while MOSFETs M1 and M4 operate as current sources. The current sources, M1 and M4, limit the current available to the inverter, M2 and M3; in other words, the inverter is starved for the current. The MOSFETs M5 and M6 drain currents are the same and are set by input control voltage, which is varied in the steps of 0.5V, starting with 5V. The currents in M5 and M6 are mirrored in each inverter/current source stage. There are in total 23 transistors, where upper PMOS transistors are connected to the gate of M6 and source voltage is applied to the gates of all lower NMOS transistors [9].

Figure (3) Schematic Circuit of Current-Starved VCO

# V. Phase Frequency Detector

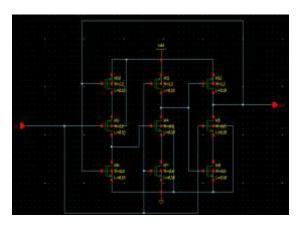

A phase frequency detector (PFD), is a device which compares the phase of two input signals and provides a signal in the form of phase error. It has two inputs which correspond to two different input signals, usually one from a current starved voltage-controlled oscillator and other is a reference source. It has two outputs which instruct subsequent circuitry on how to adjust to lock onto the phase [10].

From Figure (4) the Schematic Circuit of Phase Frequency Detector compares the leading edges of data and data1 (data is the input signal to PFD, data1 is considered as the feedback signal from the output of VCO to PFD). A data1 rising edge cannot be present without a data rising edge. If the rising edge of the data leads the data1 rising

edge, the "Up" output of the phase detector goes high while the "Down" output remains low. This causes the data1 frequency to increase and makes the edges move closer. If the data1 signal leads the data, "Up" remains low while the "Down" goes high. And we can find the phase difference between data1 and data.

There are several characteristic of PFD which can be described as below[7]:

- A rising edge from the data and data1 must be present when doing a phase comparison.

- The width of the data1 and the data is irrelevant.

- The output of the "Up" and "Down" of the PFD are both low when the circuit is locked.

Figure (4) Schematic Circuit of Phase Frequency Detector

# VI. CHARGE PUMP

A charge pump circuit is used to convert the digital signal from the phase frequency detector to analog signal, the output of which is used to control the frequency of the voltage control oscillator. The output of the PFD should be combined into a single output to drive the loop filter. In Figure (5) charge pump, two NMOS and two PMOS are connected serially. The uppermost PMOS and lowermost NMOS are considered as the current source and the other PMOS and NMOS in the middle are connected to the "Up" and "Down" of the output of PFD, respectively When the PFD "Up" signal goes high, the PMOS will turn on. This will connect the current source to the loop filter. It is in the similar way when the PFD "Down" signal goes high.

Figure (5) Schematic Circuit of Charge Pump

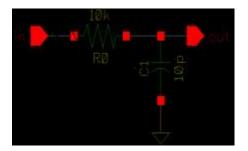

# VII. LOOP FILTER

The function of the loop filter is to convert the output signal of phase frequency detector to control voltage and also to filter out any high frequency noise introduced by the PFD. The loop filter shown in Figure (6) used with this type of PFD is a simple RC low-pass filter. Since the output of the PFD is oscillating, the output of the loop filter will show a ripple as well, even when the loop is locked. This modulates the clock frequency, an unwanted characteristic of a DPLL using PFD. A ripple on the output of the loop filter with a frequency equal to the clock frequency will modulate the control voltage of the VCO. A high speed low power consumption positive edge triggered Delayed (D) flip-flop was designed for increasing the speed of counter in Phase locked loop, using 180 nm CMOS technology.

Figure (6): Low Pass Filter

## VIII. FREQUENCY DIVIDER

Frequency divider divides the VCO frequency to generate a frequency which is comparable with reference frequency. Here we used divide by 2 network, we can vary the divider network for synthesis of different frequencies. It divide the clock signal of VCO and generate clock as shown in figure (7), than applied to phase frequency detector which compare it with input data[12].

Figure (7) Schematic Circuit of Frequency divider

# IX. RESULTS AND WAVEFORMS

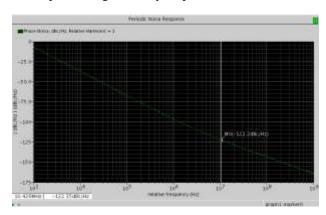

The PLL for high performance application have been designed using 180 nm CMOS technology with 36.516 mA and emulated by Zeni Electronic Design Automation. The phase noise obtained is-122.2 dBc/Hz @ 10 MHz offset frequency, which is shown in Fig. (8) The proposed voltage

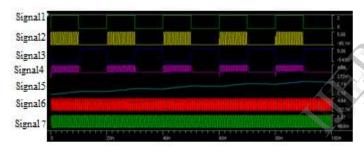

controlled oscillator has designed for getting optimized 2.2 GHz frequency. A design has been completed with 180 nm CMOS technology and 1.5 Volt supply voltage. The final output waveform of complete PLL is shown in Figure (9). Where signal1 is for input data signal, signal2 is for output of PFD UP signal, signal3 is for output of PFD DN signal, signal4 is output charge pump, signal5 is output of Low Pass Filter, signal6 is output of current starved voltage controlled oscillator, and signal7 is output of divider circuit which is performing divide by 2 operation.

Figure (8): Phase noise response of CSVCO @10 MHz offset frequency

Figure (9): waveforms of different stages of output signal for PLL

### X. CONCLUSION

Modern wireless communication system employ phase locked loop (PLL) mainly on synchronization clock synthesis, skew and jitter reduction. Because in the increase of speed of the circuit operation, there is a need of a PLL circuit with faster locking ability. The PLL has been designed with low power, small chip size area and better phase noise using 180 nm CMOS technology for high performance PLL and simulated by ZENI- EDA environment. While increasing the number of stages for getting the higher frequency the power dissipation and size of oscillator was going to increase. Hence instead of increasing the number of stages and time constant again a control voltage and width of the CMOS can be adjusted for getting the higher frequency.

# **REFERENCES**

[1] J. Craninckx and M. Steyaert, "A 1.8-GHz low-phase noise CMOS VCO using optimized hollow spiral inductors," IEEE J. Solid-State Circuits, vol. 32, pp. 736-744, May 1997.

- Yalcin, A.E. and P. John, 2004. A 5.9-GHz voltage controlled ring [2] oscillator in 0.18 um CMOS technology. IEEE J. Solid-State Circuit, 39(1): 230-233.

- C. H. Park and B. Kim, "A low-noise, 900-MHz VCO in 0.6-\_m [3] CMOS," IEEE J. Solid-State Circuits, vol. 34, pp. 586-591, May

- [4] A. Hajimiri, S. Limotyrakis, and T. H. Lee, "Phase noise in multigigahertz CMOS ring oscillators," in Proc. IEEE 1998 Custom Integrated Circuit Conf., 1998, pp. 49-52.

- [5] T. Friedrich, "Direct phase noise measurements using a modern spectrum analyzer," Microwave J., vol. 35, pp. 94, 96, 99, 101–104,

- K. M. Ring and S. Krishnan, "Long-term jitter reduction through [6] supply noise compensation," in Proceedings of the IEEE International Symposium on Circuits and Systems (ISCAS'08), pp. 2382–2385, Seattle, Wash, USA, May 2008. Y. Chen, Z. Wang, and L. Zhang, "A 5GHz 0.18-µm CMOS

- [7] technology PLL with a symmetry PFD," in Proceedings of the International Conference on Microwave and Millimeter Wave Technology (ICMMT'08), vol. 2, pp. 562-565, Nanjing, China, April 2008.

- [8] Rahajandraibe, A.W., L. Zaid, V.C. de Beaupre and J. Roche, 2007. Low-gain-wide-range 2.4-GHz phase locked loop. 14th IEEE International Conference on Electronics, Circuits and Systems, pp:

- [9] S. B. Rashmi and Siva S. Yellampalli, "Design of Phase Frequency Detector and Charge Pump for High Frequency PLL," International Journal of Soft Computing and Engineering, vol.2, Issue-2, May 2012, pp 88-92.

- V.Lule and V.Nasre, "Area efficient 0.18um CMOS phase frequency detector for high speed PLL", International Journal of [10] Engineering Scientific and Research Publication, vol.2, Feb.2012, pp 1-3.

- Chakra borty, B. and R.R. Pal, 2007. Study of speed enhancement of a CMOS ring VCO. J. Phys. Sci., 11: 77-86.

- Kashyap K. Patel, Nilesh D. Patel, "Phase Frequency Detector and Charge Pump For DPLL Using 0.18µm CMOS Technology" International Journal of Emerging Technology and Advanced Engineering , ISSN 2250-2459, ISO 9001:2008 Certified Journal, Volume 3 Issue1, Page No. 55-58, January 2013)

- [13] Kruti P. Thakore, Harikrishna C. Parmar, Dr. N.M. Devashrayee, ' High Speed PFD with Charge Pump and Loop Filter for Low Jitter and Low Power PLL", IJECT Vol. 2, Issue 2, June 2011.

- Kruti P. Thakore, Dr. D. J. Shah "Design and Implementation of Low Power and Low Jitter PLL "Laljibhai Chaturbhai Institute [14] of Technology" Bhandu-384120, 13-14, April-2012

- [15] Darji Urvi M. "Design, Analysis and implementation of DPLL using 0.18µm CMOS Technology " Gujarat Technological University May-June 2012

- M. Behbahani and G. E. R. Cowan, "Phase-Noise tunable ring [16] voltage-controlled oscillator in 90 nm CMOS," IEEE MWSCAS 2013, pp.1031-1034, Aug. 2013.

- J. Lee, M. Liu, and H. Wang, "A 75 GHz Phase-Locked Loop in [17] 90-nm CMOS Technology," IEEE Journal of Solid-State Circuits, vol. 43, no. 6, pp. 1414–1426, June 2008.

- H. R. Rategh, H. Samavati, and T. Lee, "A CMOS Frequency [18] Synthesizer with an Injection-locked Frequency Divider for a 5-GHz Wireless LAN Receiver," IEEE Journal of Solid-State Circuits, vol. 35, no. 5, pp. 780–787, May 2000.

- [19] N. Dalt, S. Derksen, P. Greco, C. Sandner, H. Schmid, and K. Strohmayer, "A Fully Integrated 2.4-GHz LC-VCO Frequency Synthesizer With 3-ps Jitter in 0.18-µm Standard Digital CMOS Copper Technology," IEEE Journal of Solid-State Circuits, vol. 37, no. 7, pp. 959-962, July 2002.

- [20] R. van de Beek, C. Vaucher, D. Leenaerts, E. Klumperink, and B. Nauta, "A 2.5-10 GHz Clock Multiplier Unit with 0.22-ps RMS Jitter in Standard 0.18-μm CMOS," IEEE Journal of Solid-State Circuits, vol. 39, no. 11, pp. 1862-1872, November 2004.

- [21] A. Ng, G. Leung, K.-C. Kwok, and H. C. Luong, "A 1-V 24-GHz 17.5-mW Phase-Locked Loop in a 0.18-µm Process," IEEE Journal of Solid-State Circuits, vol. 41, no. 6, pp. 1236-1244, June 2006.

[11]

[12]