# Space Vectors Modulation for Dual Output Converters

K.L.N.Chaitanya <sup>1</sup> PG Student CMR College of engg & technology K.Srividya Savitri <sup>2</sup>

Assistant Professor

CMR College of engg & technology

R.Shirisha <sup>3</sup>

Assistant Professor

CMR College of engg & technology

Abstract—Recently, nine-switch inverter and nine-switch-zsource inverter have been proposed as dual output inverters. In this paper, the space vector modulation (SVM) of nine-switch inverter and nine-switch-z-source inverter is proposed. The proposed method increases the sum of modulation indices up to 15% in contrast with the conventional, scheme in which the sum of modulation indices is equal or less than one. The extra voltage available for a given input dc-voltage, translates to a higher torque—a critical factor for defining the capacity of products in marketplace. Also, in order to further reduce the cost of power devices and also thermal heat effect, and to reduce the number of semiconductor switching, specific SVM switching pattern is presented. This feature will be advantageous for high-power inverter applications where cost and efficiency are key decision factors. Furthermore, a novel SVM is proposed for minimizing total harmonic distortion. The performance of the proposed SVM for both nine-switch inverter and nine-switch-z-source inverter is verified by simulation. Experimental results validate the simulation results as well as the superiority of the proposed SVM.

Index Terms—Nine-switch inverter, nine-switch-z-source inverter, space vector modulation (SVM).

## I. INTRODUCTION

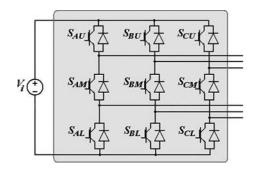

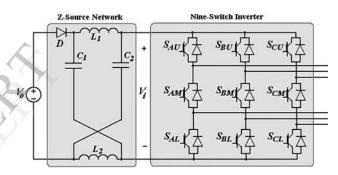

NVERTERS are used as dc/ac converter and power controller for ac load such as motor drivers. In many cases, there are two or more ac loads, which require independent control. The conventional solution is to use separate inverters. This increases cost and volume of system. A dual output inverter has been presented in [1] using only nine semiconductor switches (see Fig. 1). This inverter is known as nine-switch inverter and is also used as an ac/ac converter in [2] and [3]. The nine-switch inverter is composed of two conventional inverters with three common switches. In nine-switch inverter, sum of modulation index of two outputs must be less than or equal to one. Therefore, voltage amplitude of outputs is smaller, compared with two separate inverters [4]. To remedy this problem, this paper proposes using an impedance source (z-source) network in front of nine-switch inverter as a dc/dc boost converter (see Fig. 2). Z-source network was used as front-end boost converter for a conventional inverter in [5], for the first time. This inverter was called z-source inverter and has been proposed for fuel cell, photovoltaic, and wind turbine systems [6]–[8]. The z-source network also was used in other converters such as three-level inverters [9], [10].

In [1], carrier-based pulsewidth modulation (PWM) methods have been proposed for nine-switch inverter. This paper proposes space vector modulation (SVM) methods for the aforementioned nine-switch and nine-switch-z-source inverters

Fig. 1. Nine-switch inverter.

Fig. 2. Nine-switch-z-source inverter.

. In order to reduce number of semiconductor switching and total distortion harmonic (THD), some specific switching patterns for SVM are proposed.

This paper is organized as follows. Section II describes the carrier-based PWM control method for nine-switch inverter. Section III describes the proposed SVM for nine-switch inverter, as well as two special SVMs with minimum switching number and THD. The proposed SVM is developed for nine-switch-z-source inverter in Section IV. Section V describes maximum gain. Finally, Section VI presents simulation and experimental results.

## II. CARRIER-BASED PWM METHOD

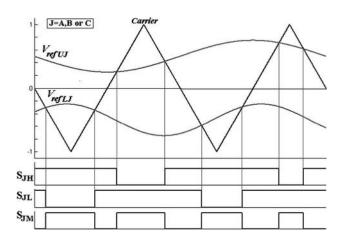

The carrier-based PWM control method for nine-switch inverter is shown in Fig. 3. There are two reference signals (upper and lower) for each phase. The upper and lower reference signals are related to upper and lower outputs respectively. The

TABLE I SEMICONDUCTORS ON-OFF POSITION OF LEGS

|    | $S_{JU}$ | $S_{JM}$ | $S_{JL}$ |

|----|----------|----------|----------|

| 1  | ON       | OFF      | ON       |

| 0  | OFF      | ON       | ON       |

| -1 | ON       | ON       | OFF      |

| $V_{Z}$        | $V_{\!\!AU}$   | $V_{AU}$       | V <sub>Z</sub> | V <sub>AU</sub> | V <sub>AU</sub> | V <sub>Z</sub> | V <sub>AL</sub> | $V_{\!\!AL}$   | $V_{\rm Z}$    | V <sub>AL</sub> | $V_{AL}$       | $V_{Z}$        |

|----------------|----------------|----------------|----------------|-----------------|-----------------|----------------|-----------------|----------------|----------------|-----------------|----------------|----------------|

| T <sub>0</sub> | T <sub>1</sub> | T <sub>2</sub> | T <sub>0</sub> | T <sub>2</sub>  | Tı              | T <sub>0</sub> | T <sub>3</sub>  | T <sub>4</sub> | T <sub>0</sub> | T <sub>4</sub>  | T <sub>3</sub> | T <sub>0</sub> |

Fig. 5. Typical SVM switching vector sequence.

TABLE II SVM Switching Vectors

| Vector | Leg A | Leg B | Leg C | Type         |

|--------|-------|-------|-------|--------------|

| 1      | 1     | 0     | 0     |              |

| 2      | 1     | 1     | 0     |              |

| 3      | 0     | 1     | 0     | Upper Active |

| 4      | 0     | 1     | 1     |              |

| 5      | 0     | 0     | 1     |              |

| 6      | 1     | 0     | 1     |              |

| 7      | -1    | 1     | 1     |              |

| 8      | -1    | -1    | 1     |              |

| 9      | 1     | -1    | 1     | Lower Active |

| 10     | 1     | -1    | -1    |              |

| _ 11   | 1     | 1     | -1    |              |

| 12     | -1    | 1     | -1    |              |

| 13     | 1     | 1     | 1     | Zero         |

| 14     | 0     | 0     | 0     |              |

| 15     | -1    | -1    | -1    |              |

Fig. 3. Carrier-based PWM method for nine-switch inverter.

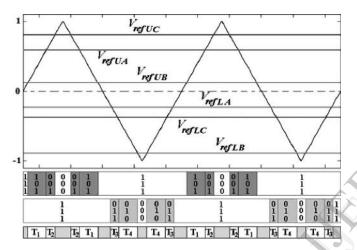

Fig. 4. Carrier-based PWM method switching vector.

gate signal for upper switch of a leg is generated by comparing the carrier signal and upper reference signal of the related phase  $(V_{\text{ref}UJ})$ . Similarly, the gate signal for lower switch is generated from the carrier signal and lower reference signal of the related phase  $(V_{\text{ref}LJ})$ . The gate signal for mid switch is generated by the logical XOR of the gate signals for upper and lower switches. With this method, always two switches are ON in each leg.

Fig. 4 shows carrier-based PWM method switching vectors. There are six vectors in each switching cycle for both outputs: two nonzero vectors, one zero vector  $0\ 0\ 0$ , two nonezero vectors and one zero vector  $1\ 1\ 1$  {two active—short zero  $(0\ 0\ 0)$ —two active—long zero  $(1\ 1\ 1)$ }. In an active vector, output load is connected to the dc input source, while in a zero vector, the output load is short-circuited. When one of the outputs has an active or short zero  $(0\ 0\ 0)$  vector, the other output has long zero  $(1\ 1\ 1)$  vector.

## III. SVM FOR NINE-SWITCH INVERTER

In regard to Fig. 3, each leg can be in three different semi-conductors ON-OFF position. These position can be called  $\{1\}$ ,  $\{0\}$ , and  $\{-1\}$ , as is illustrated in Table I. In Table I, J refers to leg A, B, or C and U, M, L refers to upper, mid, and lower semiconductor, respectively.

The combination of switching vector of both outputs in Fig. 4 creates a specific sequence as shown in Fig. 5. This sequence is used to design SVM method. There are 12 vectors in each switching cycle: {two upper active  $(V_{AU})$ —zero  $(V_Z)$ —two upper active  $(V_{AU})$ —zero  $(V_Z)$ —two lower active  $(V_{AL})$ —zero  $(V_Z)$ . The switching vectors are listed in Table II. The vectors  $V_1$ – $V_6$  are upper active vectors. In these vectors, the upper output is in active state, and the lower output is in zero state. There is an inverse logic in lower active vectors  $(V_7$ – $V_{12})$ . In zero vectors  $(V_{13}$ – $V_{15})$ , both outputs are in zero state.

Table II does not include all possible variations of switching states  $\{1\}$ ,  $\{0\}$ , and  $\{-1\}$ . Since a vector including  $\{-1\}$  and  $\{0\}$  connects both loads to the dc source at the same time, the loads lose their independence and they cannot have independent frequencies. This is the reason for avoiding a vector that includes combinations of  $\{-1\}$  and  $\{0\}$ .

In none of the switching vectors as listed in Table II, both outputs are not in an active state at the same time. However, in vectors including both  $\{-1\}$  and  $\{0\}$  such as  $\{-1, 1, 0\}$ , both outputs are in active state. These vectors are ignored because there are not all combinations of active vectors for both outputs. For example, if upper output be in active vector  $(1\ 1\ 0)$ , lower output can be in vectors  $(0\ 0\ 0)$ ,  $(1\ 0\ 0)$ ,  $(0\ 1\ 0)$ , or  $(1\ 1\ 0)$  as shown in Fig. 6. However, vectors  $(0\ 1\ 1)$ ,  $(0\ 0\ 1)$ , and  $(1\ 0\ 1)$  are not available for lower output. Therefore, outputs cannot be controlled independently.

Fig. 6. Available switching vectors of nine-switch inverter while upper output is in active vector (1 1 0).

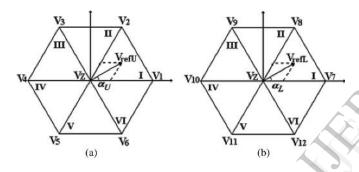

Fig. 7. Space vector diagrams for nine-switch inverter. (a) Upper output. (b) Lower output.

To determine the proper active vectors, two space vector diagrams are proposed as shown in Fig. 7. The diagrams (a) and (b) are used to determine the upper and lower active vectors, respectively. The SVM active vectors are determined with regard to location of upper reference signal  $(V_{ref}U)$  in the diagram (a) and lower reference signal ( $V_{\text{ref}L}$ ) in the diagram (b). The reference signals for the upper and lower outputs are defined as

$$\overline{V}_{\text{ref}U} = V_{\text{ref}U} - \alpha_U \tag{1}$$

$$\overline{V}_{\text{ref}L} = V_{\text{ref}L} - \alpha_L \tag{2}$$

where

$$\alpha_U = 2\pi f_U t + \varphi_U \tag{3}$$

$$\alpha_L = 2\pi f_L t + \varphi_L \tag{4}$$

where  $f_U$  ,  $f_L$  are the frequencies, and  $\varphi_U$  ,  $\varphi_L$ phases. All zero vectors  $V_{13}$ ,  $V_{14}$ , and  $V_{15}$  can be used for zero states. The type of zero vectors can be selected based on control goals and optimizations such as minimum number of semiconductor switchings.

The switching time intervals of vectors are calculated as

$$T_1 = \frac{3}{2} m_U T \sin \frac{\pi}{3} - \alpha_U$$

(5) just vec www.ijert.org

| I               | ref U                 | in I           | . Ш от               | ·v             |                           | $V_{ref}$        | L in             | і, ш             | or V           |                  |

|-----------------|-----------------------|----------------|----------------------|----------------|---------------------------|------------------|------------------|------------------|----------------|------------------|

| $V_{13}$        | $V_{AU_2}$            | $V_{AU_{l}}$   | $V_{AU_l}$           | $V_{AU_2}$     | V <sub>13</sub>           | V <sub>AL1</sub> | $V_{\!\!\!AL_2}$ | $V_{AL_2}$       | $V_{AL_1}$     | $V_{13}$         |

| $\frac{T_0}{2}$ | T <sub>2</sub>        | T <sub>1</sub> | T <sub>1</sub>       | T <sub>2</sub> | T <sub>e</sub>            | T <sub>3</sub>   | T <sub>4</sub>   | T <sub>4</sub>   | T <sub>3</sub> | $\frac{T_0}{2}$  |

| ı               | ref U                 | in 11          | , IV o               | r VI           | $V_{refL}$ in I, III or V |                  |                  |                  |                |                  |

| $V_{13}$        | $V_{AU_1}$            | $V_{AU_2}$     | $V_{AU_2}$           | $V_{\!\!AU_1}$ | $V_{13}$                  | VALI             | $V_{\!\!AL_2}$   | $V_{\!\!AL_2}$   | $V_{\!\!AL_1}$ | $V_{13}$         |

| $\frac{T_0}{2}$ | Tı                    | T <sub>2</sub> | T <sub>2</sub>       | T <sub>1</sub> | T <sub>0</sub>            | T <sub>3</sub>   | T <sub>4</sub>   | T <sub>4</sub>   | T <sub>3</sub> | T <sub>0</sub> 2 |

|                 | $V_{ref U}$           | in             | I, III o             | r V            |                           | $V_{refL}$       | , in             | II, IV           | or V           | 1                |

| $V_{13}$        | $V_{AU_2}$            | $V_{AU_{l}}$   | $V_{\!\!AU_{\!\!1}}$ | $V_{AU_2}$     | $V_{13}$                  | V <sub>AL2</sub> | $V_{\!\!AL_1}$   | $V_{\!\!A\!L_1}$ | $V_{\!\!AL_2}$ | $V_{13}$         |

| $\frac{T_0}{2}$ | T <sub>2</sub>        | T <sub>l</sub> | T <sub>1</sub>       | T <sub>2</sub> | T <sub>0</sub>            | T <sub>4</sub>   | T <sub>3</sub>   | T <sub>3</sub>   | T <sub>4</sub> | T <sub>0</sub> 2 |

|                 | $V_{\mathit{ref}\ U}$ | in I           | I, IV o              | r VI           |                           | $V_{refl}$       | in               | п, гv            | or VI          | 1                |

| $V_{13}$        | $V_{AU_1}$            | $V_{AU_2}$     | V <sub>AU2</sub>     | $V_{AU_1}$     | $V_{13}$                  | V <sub>AL2</sub> | $V_{\!\!AL_1}$   | $V_{AL_1}$       | $V_{AL_2}$     | $V_{13}$         |

| $\frac{T_0}{2}$ | Tı                    | T <sub>2</sub> | T <sub>2</sub>       | T <sub>1</sub> | T <sub>0</sub>            | T <sub>4</sub>   | T <sub>3</sub>   | T <sub>3</sub>   | T <sub>4</sub> | $\frac{T_0}{2}$  |

Fig. 8. SVM with reduced number of semiconductor switching.

$$T_{2} = \frac{\sqrt{\frac{3}{3}}}{2} m_{U} T \sin(\alpha_{U})$$

$$T_{3} = \frac{\sqrt{\frac{3}{3}}}{2} m_{L} T \sin \frac{\pi}{3} - \alpha_{L}$$

$$(6)$$

$$T_3 = \frac{\sqrt{3}}{2} m_L \ T \sin \ \frac{\pi}{3} - \alpha_L \tag{7}$$

$$T_4 = \frac{\sqrt{3}}{2} m_L \ T \sin(\alpha_L) \tag{8}$$

$$T_o = T - T_1 - T_2 - T_3 - T_4 \tag{9}$$

where  $T_1$ ,  $T_2$  are the time interval of upper active vectors,  $T_3$ ,  $T_4$ are time of lower active vectors,  $T_o$  is time of zero vectors and Tis switching period.  $m_U$  and  $m_L$  are upper and lower modulation indices, respectively, and defined by

$$m_U = 2\frac{V_{\text{ref}U}}{V_i} \tag{10}$$

$$m_L = 2 \frac{V_{\text{ref}L}}{V_i}.$$

(11)

The sum of active vector time intervals must be less or equals to T. Thus, the following constrain must be satisfied (see Appendix):

$$(m_U + m_L) \le \frac{2}{3} \approx 1.155.$$

(12)

Equation (12) clearly indicates that in the proposed SVM scheme, sum of modulation indices increases about 15%—a very important feature to provide higher torque for a given input dc-voltage. In the case of washing machines, the above capability translates to higher machine capacity (in terms of cloth load) at high spin speed (e.g., 1800 r/min)—an important product feature in marketplace.

A switching vector sequence for the proposed SVM is shown in Fig. 8. This switching sequence is developed to reduce the number of semiconductor switching. The zero vectors are placed just between two upper and lower active vectors. In upper active vectors, legs are in state {1} or {0} and in lower active vectors,

TABLE III

SHOOT-THROUGH VECTORS OF NINE-SWITCH Z-SOURCE INVERTER

| Vector | Leg A | Leg B | Leg C |

|--------|-------|-------|-------|

| 16     | 2     | 2     | 2     |

| 17     | 2     | 2     | 0     |

| 18     | 2     | 2     | 1     |

| 19     | 2     | 2     | -1    |

| 20     | 2     | 0     | 2     |

| 21     | 2     | 1     | 2     |

| 22     | 2     | -1    | 2     |

| 23     | 0     | 2     | 2     |

| 24     | 1     | 2     | 2     |

| 25     | -1    | 2     | 2     |

| 26     | 2     | 0     | 0     |

| 27     | 2     | 1     | 1     |

| 28     | 2     | -1    | -1    |

| 29     | 0     | 2     | 0     |

| 30     | 1     | 2     | 1     |

| 31     | -1    | 2     | -1    |

| 32     | 0     | 0     | 2     |

| 33     | 1     | 1     | 2     |

| 34     | -1    | -1    | 2     |

TABLE IV on-off Position of Semiconductor Switches in State  $\{2\}$

$S_{JM}$

ON

$S_{JL}$

ON

$S_{JU}$

ON

|                           | I or Y         | І, П           | in             | ref L          | 1                  |                | 7                  | I or V           | 1. П             | in               | V <sub>ref U</sub> |                    |                 |

|---------------------------|----------------|----------------|----------------|----------------|--------------------|----------------|--------------------|------------------|------------------|------------------|--------------------|--------------------|-----------------|

| SCL V13                   | $V_{AL_1}$     | $V_{AL_2}$     | $V_{AL_2}$     | $V_{AL_1}$     | V <sub>SCL</sub>   |                |                    |                  |                  |                  | $V_{AU_2}$         | Vscu               | V <sub>13</sub> |

| sc/2<br>T <sub>e</sub> /2 | T <sub>3</sub> | T <sub>4</sub> | T4             | T <sub>3</sub> | T <sub>SC</sub> /2 | T.             | T <sub>SC</sub> /2 | T <sub>2</sub>   | T <sub>1</sub>   | Tı               | T <sub>2</sub>     | T <sub>SC</sub> /2 | 1               |

|                           | or V           |                |                |                |                    |                |                    |                  |                  | in               |                    |                    |                 |

| SCL V13                   | $V_{AL_1}$     | $V_{AL_2}$     |                |                |                    |                | Vscu               | V <sub>AU1</sub> | V <sub>AU2</sub> | V <sub>AU2</sub> | $V_{AU_1}$         | Vscu               | V <sub>13</sub> |

| sc/2<br>T <sub>o</sub> /2 | T <sub>3</sub> | T <sub>4</sub> | T <sub>4</sub> | T <sub>3</sub> | T <sub>SC</sub> /2 | T.             | T <sub>SC</sub> /2 | Tı               | T <sub>2</sub>   | T <sub>2</sub>   | T <sub>1</sub>     | T <sub>SC</sub> /2 | 1               |

|                           | or V           | п, г           | in             | ref L          | ν                  |                |                    | or V             | і. ш             | in               | ref U              | ı                  |                 |

| SCL V13                   | $V_{AL_2}$     | $V_{AL_1}$     | $V_{AL_1}$     | $V_{AL_2}$     | V <sub>SCL</sub>   | $V_{13}$       | Vscu               | $V_{AU_2}$       | $V_{AU_1}$       | $V_{AU_1}$       | V <sub>AU2</sub>   | Vscu               | V <sub>13</sub> |

| sc/2<br>T <sub>o</sub> /2 | T4             | T <sub>3</sub> | T <sub>3</sub> | T4             | T <sub>SC</sub> /2 | T <sub>o</sub> | T <sub>SC</sub> /2 | T <sub>2</sub>   | T <sub>1</sub>   | T <sub>1</sub>   | T <sub>2</sub>     | T <sub>SC</sub> /2 | 1               |

|                           | T <sub>4</sub> |                | T <sub>3</sub> | T4             | T <sub>SC</sub> /2 |                |                    | T <sub>2</sub>   | T <sub>1</sub>   | T <sub>1</sub>   | T <sub>2</sub>     | T <sub>SC</sub> /2 |                 |

Fig. 10. Nine-switch-z-source inverter SVM with reduced switching.

$V_{AU_1}$

when the inverter has a zero state. Table III shows all the vectors that the inverter includes zero state and the z-source network has a shoot-through state. These vectors are known as shoot-through vectors. There is a new state (state {2}) in Table III. The ON-OFF position of switches of a leg in state {2} is shown in Table IV. All vectors of Table III can be used for generating

| $V_{re}$       | fU i           | n I. III        | or V             |                | Į                | ref L            | in I,          | Ш or             | v                  |

|----------------|----------------|-----------------|------------------|----------------|------------------|------------------|----------------|------------------|--------------------|

| $V_{AU_2}$     | $V_{AU_l}$     | V <sub>14</sub> | V <sub>AU1</sub> | $V_{AU_2}$     | $V_{\!\!AL_1}$   | $V_{\!\!\!AL_2}$ | $V_{15}$       | V <sub>AL2</sub> | $V_{\!\!\!AL_1}$   |

| T <sub>2</sub> | T <sub>1</sub> | T <sub>e</sub>  | T <sub>1</sub>   | T <sub>2</sub> | T <sub>3</sub>   | T <sub>4</sub>   | T <sub>0</sub> | T <sub>4</sub>   | T <sub>3</sub>     |

| $V_{res}$      | f U in         | а п, г          | or VI            |                | ı                | ref L            | in I,          | Ш or             | v                  |

| $V_{AU_1}$     |                | V <sub>14</sub> | V <sub>AU2</sub> | $V_{AU_1}$     |                  |                  | $V_{15}$       | V <sub>AL2</sub> | $V_{AL_1}$         |

| T <sub>1</sub> | T <sub>2</sub> | T <sub>o</sub>  | T <sub>2</sub>   | T <sub>1</sub> | T <sub>3</sub>   | T <sub>4</sub>   | T <sub>0</sub> | T <sub>4</sub>   | T <sub>3</sub>     |

| $V_{i}$        | ef U           | in I, I         | □ or V           |                | ν                | ref L            | in II,         | IV or            | VI                 |

| $V_{AU_2}$     | $V_{AU_1}$     | $V_{14}$        | V <sub>AU1</sub> | $V_{AU_2}$     | $V_{\!\!\!AL_2}$ | $V_{\!\!AL_1}$   | $V_{15}$       | $V_{AL_1}$       | $V_{\!\!\!\!AL_2}$ |

| T <sub>2</sub> | T <sub>1</sub> | T <sub>0</sub>  | T <sub>1</sub>   | T <sub>2</sub> | T <sub>4</sub>   | T <sub>3</sub>   | T <sub>0</sub> | T <sub>3</sub>   | T <sub>4</sub>     |

| $V_{r}$        | <i>ef U</i> j  | in Π, Γ         | V or V           | I              | ν                | ref L            | in П,          | IV or            | VI                 |

| $V_{AU_1}$     | $V_{AU_2}$     | $V_{\mu}$       | V <sub>AU2</sub> | $V_{AU_1}$     |                  |                  | $V_{15}$       | $V_{AL_1}$       | $V_{AL_2}$         |

|                |                |                 |                  |                |                  |                  |                |                  |                    |

$T_2 \mid T_1 \mid$

Fig. 9. SVM with reduced THD.

legs are in state  $\{1\}$  or  $\{-1\}$ . If  $V_{13}$  zero vector is placed between the active vectors, minimum number of switching is required. While if  $V_{14}$  or  $V_{15}$  zero vectors are used, number of switching is increased.

T<sub>4</sub> | T<sub>3</sub>

There are two odd active vectors  $(V_1, V_3, V_5, V_8, V_{10},$  and  $V_{12})$  and two even active vectors  $(V_2, V_4, V_6, V_7, V_9,$  and  $V_{11})$  in a switching sequence. In an even active vector, two legs are in state  $\{1\}$ , while in an odd active vector only one leg is in state

$\{1\}$ . If even active vectors are placed next to  $V_{13}$ , number of switching will be reduced even more (see Fig. 8).

There are other possible switch generation methods too, e.g., a switching method, to reduce THD. To minimize THD, active vectors for each output should be centrally placed within the switching period [11]. Fig. 9 shows a switching vector sequence that shifts active vector into center of switching period, hence reducing THD. In this sequence, zero vectors are inserted between active vectors. In Fig. 9,  $V_{14}$  is inserted between upper active vectors and  $V_{15}$  is inserted between lower active vectors.

# IV. NINE-SWITCH-Z-SOURCE INVERTER SVM

The nine-switch-z-source inverter is shown in Fig. 2. This inverter has an extra z-source network including two inductors  $(L_1 \text{ and } L_2)$ , two capacitors  $(C_1 \text{ and } C_2)$  and a diode (D). The z-source network is similar to a dc/dc boost converter with [12]

$$V_i = B \ V_o \tag{13}$$

where  $V_o$  is input dc voltage and  $V_i$  is output of z-source network. B is known as boost factor and is given by following equation:

$$B = \frac{1}{1 - 2(T_{\rm SC}/T)} \tag{14}$$

where  $T_{\rm SC}$  is shoot-through time. In the shoot-through times, the output of z-source network is shorted through the switches of the inverter. During shoot-through state, since the inverter (output of z-source network) is shorted, inverter cannot have an active vector. Therefore a shoot-through state can only occur

a shoot-through state.

Fig. 10 shows a SVM vector sequence for nine-switch inverter with reduced number of switching. The sequence is a modified version of Fig. 8. Two shoot-through vectors are placed in both sides of zero vector ( $V_{13}$ ). Here, the shoot-through vector close to upper active vector is called upper shoot-through vector ( $V_{\rm SCU}$ ) and the shoot-through vector close to lower ent.org

TABLE V

DETERMINING UPPER AND LOWER SHOOT-THROUGH VECTOR WITH REDUCED NUMBER OF SWITCHING

| Section of V <sub>refU</sub> | $V_{SCU}$       | Section of V <sub>refL</sub> | $V_{SCL}$     |

|------------------------------|-----------------|------------------------------|---------------|

| I                            | V <sub>33</sub> | I                            | $V_{27}$      |

| п                            | $V_{33}$        | II                           | $V_{3\theta}$ |

| Ш                            | $V_{27}$        | III                          | $V_{3\theta}$ |

| IV                           | $V_{27}$        | IV                           | $V_{33}$      |

| V                            | $V_{3\theta}$   | V                            | $V_{33}$      |

| VI                           | $V_{3\theta}$   | VI                           | $V_{27}$      |

| 25               | ı                | ref U              | in I.           | Шor                | v                | 385 J            | 92             | ı                     | ref L              | in I            | , III or           | v              |                |

|------------------|------------------|--------------------|-----------------|--------------------|------------------|------------------|----------------|-----------------------|--------------------|-----------------|--------------------|----------------|----------------|

| VAU2             | $V_{AU_1}$       | Vscu               | $V_{14}$        | Vscu               | V <sub>AU1</sub> | $V_{AU_2}$       | $V_{AL_1}$     | $V_{AL_2}$            | $V_{SCL}$          | $V_{15}$        | V <sub>SCL</sub>   | $V_{AL_2}$     | $V_{AL_1}$     |

| T <sub>2</sub>   | T <sub>1</sub>   | T <sub>SC</sub> /2 | T,              | T <sub>SC</sub> /2 | T <sub>1</sub>   | T <sub>2</sub>   | T <sub>3</sub> | <b>T</b> <sub>4</sub> | T <sub>SC</sub> /2 | T <sub>o</sub>  | T <sub>SC</sub> /2 | T <sub>4</sub> | T <sub>3</sub> |

|                  | $\nu_{i}$        | ef U               | in II.          | . IV or            | VI               |                  |                | ν                     | ref L              | in I,           | ш or               | v              |                |

| $V_{AU_1}$       | V <sub>AU2</sub> | Vscu               | V <sub>I4</sub> | Vscu               | $V_{AU_2}$       | V <sub>AU1</sub> | $V_{AL_1}$     |                       | Vscl               | V <sub>15</sub> | Vscl               | $V_{AL_2}$     | $V_{AL_1}$     |

| T <sub>1</sub>   | T <sub>2</sub>   | T <sub>SC</sub> /2 | T,              | T <sub>SC</sub> /2 | T <sub>2</sub>   | T <sub>1</sub>   | T <sub>3</sub> | T <sub>4</sub>        | T <sub>SC</sub> /2 | T <sub>o</sub>  | T <sub>SC</sub> /2 | T <sub>4</sub> | T <sub>3</sub> |

|                  | $V_{n}$          | ef U               | in I.           | Ш or `             | v                |                  |                | $\nu$                 | ref L              | in II           | , IV or            | VI             |                |

| V <sub>AU2</sub> | VAUI             |                    | V <sub>I4</sub> | Vscu               | V <sub>AU1</sub> | V <sub>AU2</sub> | $V_{AL_2}$     |                       |                    | V <sub>15</sub> | Vscl               | $V_{AL_1}$     | $V_{AL_2}$     |

| T <sub>2</sub>   | T <sub>1</sub>   | T <sub>SC</sub> /2 | T <sub>o</sub>  | T <sub>SC</sub> /2 | T <sub>1</sub>   | T <sub>2</sub>   | T4             | T <sub>3</sub>        | T <sub>SC</sub> /2 | T <sub>o</sub>  | T <sub>SC</sub> /2 | T <sub>3</sub> | T4             |

|                  | $V_{re}$         | fU i               | n II,           | IV or              | VI               |                  |                | $V_{i}$               | ref L              | in II.          | IV or              | VI             |                |

| V <sub>AU1</sub> |                  | Vscu               | $V_{14}$        | Vscu               | V <sub>AU2</sub> | $V_{AU_1}$       | $V_{AL_2}$     |                       |                    | $V_{l5}$        | Vscl               | $V_{AL_1}$     | $V_{AL_2}$     |

| Tı               | T <sub>2</sub>   | T <sub>SC</sub> /2 | T <sub>0</sub>  | T <sub>SC</sub> /2 | T <sub>2</sub>   | T <sub>1</sub>   | T4             | T <sub>3</sub>        | T <sub>SC</sub> /2 | To              | T <sub>SC</sub> /2 | T <sub>3</sub> | T <sub>4</sub> |

Fig. 11. Nine-switch-z-source inverter SVM with reduced THD.

active vector is called lower shoot-through vector ( $V_{SCL}$ ). All

vectors listed in Table III can be used as the upper and lower shoot-through vectors. However, vectors  $V_{27}$ ,  $V_{30}$ , and  $V_{33}$  are preferred because those vectors have only one state  $\{2\}$  and need less switching. As shown in Fig. 10, even active vectors are placed close to shoot-through vectors (the reason described in Section III). In even active vectors, two legs are in state  $\{1\}$  and one leg is in state  $\{0\}$  or  $\{-1\}$ . On other hand, in shoot-through vectors  $V_{27}$ ,  $V_{30}$ , and  $V_{33}$ , two legs are in state  $\{1\}$  and one leg is in state  $\{2\}$ . To reduce the number of switching, the two legs in state  $\{1\}$  must have the same state in an even active vector and shoot-through vector close to it. Table V can be used for shoot-through vectors selection.

For reducing THD, switching sequence shown in Fig. 11 is developed for nine-switch-z-source inverter. Similar to Fig. 9, zero vectors and shoot-through vectors are inserted between similar active vectors. Table VI can be used for shoot-through vector selection with reduced THD.

### V. MAXIMUM GAIN

The magnitude of peak phase voltage of ac outputs of nineswitch inverter can be expressed by

$$V_{\rm ac}U = m_U \frac{V_i}{2} \tag{15}$$

$$V_{\text{ac}L} = m_L \frac{V_i}{2}.\tag{16}$$

TABLE VI DETERMINING UPPER AND LOWER SHOOT-THROUGH VECTOR WITH REDUCED THD

| Section of Vrefu | $V_{SCU}$ | Section of V <sub>refL</sub> | $V_{SCL}$       |

|------------------|-----------|------------------------------|-----------------|

| I                | $V_{26}$  | I                            | V <sub>34</sub> |

| П                | V 29      | II                           | $V_{34}$        |

| Ш                | $V_{29}$  | Ш                            | $V_{28}$        |

| IV               | $V_{32}$  | IV                           | $V_{28}$        |

| V                | $V_{32}$  | V                            | $V_{31}$        |

| VI               | $V_{26}$  | VI                           | $V_{3I}$        |

According to (12), in nine-switch inverter, sum of modulation indices should be smaller than 1.15. If the same amplitude for both ac outputs is desired, we have

$$V_{\text{ac}U_{\text{m ax}}} = V_{\text{ac}L_{\text{m ax}}} = \frac{V_{\text{ac}}}{2}.$$

(17)

If amplitude of one of the outputs is set to zero, maximum amplitude of other output can be increased

$$V_{\text{ac}_{\text{m ax}}} = \sqrt[V_{i}]{\frac{1}{3}} \tag{18}$$

For nine-switch-z-source inverter, the magnitude of peak phase voltage of ac outputs can be expressed by

$$V_{\text{ac}_U} = \frac{V_o}{2} \tag{19}$$

$$E_{\text{m}_U} = \frac{V_o}{2} \tag{20}$$

$$V_{\mathrm{ac}_L} = {}^2$$

$Bm_I$

The voltage gains can be defined by [13]

$$G_{II} = Bm_{II} \tag{21}$$

$$G_L = Bm_L. (22)$$

Boost factor is limited by voltage rating of semiconductor switches  $(V_S)$ . For a given voltage rating, maximum boost factor can be calculated by

$$B_{\text{max}} = \frac{V_S}{V_o}.$$

(23)

Maximum voltage gain is determined by:

$$G_{\text{max}} = B_{\text{max}} m_{\text{max}B} \tag{24}$$

where  $m_{\text{ma } xB}$  is the maximum possible modulation index, when B is at its maximum value. If the same amplitude for both ac outputs is desired  $m_{\text{ma } xB}$  can be calculated by

$$m_{\text{ma x } B} = \frac{1}{2\sqrt{3}} (1/B_{\text{max}} + 1).$$

(25)

Thus

$$G_{\text{max}} = \frac{1}{2\sqrt{3}} (B_{\text{max}} + 1). \tag{26}$$

If amplitude of one of the outputs is set to zero, maximum possible modulation index for other output can be determined

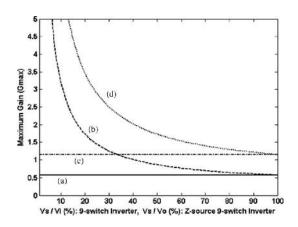

Fig. 12. Maximum voltage gain  $(G_{\text{ma x}})$  versus  $V_o$  (for nine-switch inverter) or  $V_i$  (for nine-switch-z-source inverter) for a given switch voltage rating  $(V_S)$ . (a) Nine-switch inverter: equal maximum amplitudes. (b) Nine-switch-z-source inverter: equal maximum amplitudes. (c) Nine-switch inverter: maximum am- plitude for one of the outputs. (d) Nine-switch-z-source inverter: maximum amplitude for one of the outputs.

TABLE VII

| Parameter         |                     | Value   |  |  |

|-------------------|---------------------|---------|--|--|

| Switching Free    | Switching Frequency |         |  |  |

| $f_U$             |                     | 25 Hz   |  |  |

| $f_L$             |                     | 50 Hz   |  |  |

| R <sub>load</sub> |                     | 5.6 Ohm |  |  |

| $L_f$             |                     | 1 mH    |  |  |

| $C_f$             | 40                  | 20 uF   |  |  |

| Nine-Switch       | $m_U$               | 0.35    |  |  |

| Inverter          | $m_L$               | 0.55    |  |  |

| Nine-Switch       | $m_U$               | 0.40    |  |  |

| Z-Source          | $m_L$               | 0.35    |  |  |

| Inverter          | В                   | 1.5     |  |  |

by

$$m_{\text{ma x } B} = \frac{1}{\sqrt{3}} \frac{1}{B_{\text{max}}} + 1$$

(27)

Thus

$$G_{\text{max}} = \frac{1}{3} (B_{\text{max}} + 1).$$

(28)

Fig. 12 shows maximum possible voltage gains for a given switch voltage rating.

## VI. SIMULATIONS AND EXPERIMENTAL RESULTS

The proposed SVMs are simulated for nine-switch inverter and nine-switch-z-source inverter. Prototypes of both converters also were built using DSP for verifying the proposed SVMs. Two similar resistive loads with *LC* filters are connected to the outputs of inverter. Simulation parameters are listed in Table VII.

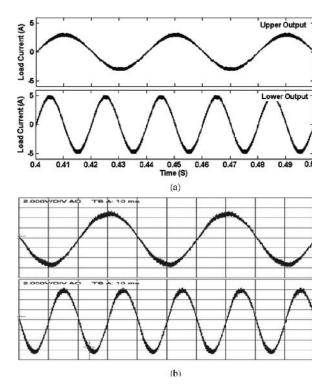

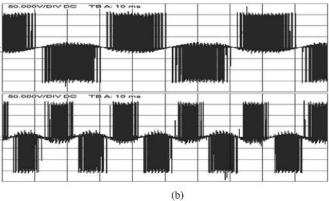

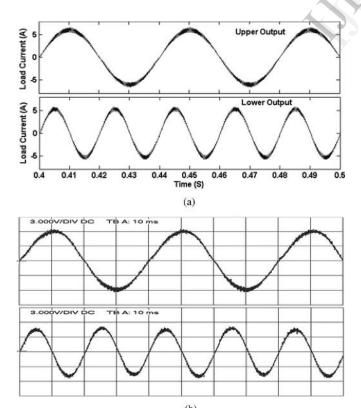

The nine-switch inverter with input dc source of 150 V is simulated and implemented with reduced number of switching SVM. Figs. 13 and 14 show line—line voltage and phase voltage of both outputs, respectively. It can be seen that both outputs have expected frequencies. The load current is shown in Fig. 15. It can be seen that the load currents have nearly sinusoidal waveforms.

Fig. 13. (a) Line voltage of nine-switch inverter (simulation). (b) Line voltage of nine-switch inverter (experimental), (50 V/DIV, 10 ms/DIV).

Fig. 14. (a) Phase voltage of nine-switch inverter (simulation). (b) Phase voltage of nine-switch inverter (Experimental), (50 V/DIV, 10 ms/DIV).

In second simulation, a z-source network including  $L_1 = L_2 = 2$  mH and  $C_1 = C_2 = 2.2$  mF was added to nineswitch inverter. An input dc source of 100 V is used. To boost input voltage to 150 V,  $T_{\rm SC}$  /T was set to 0.166 considering (14). The output of z-source network ( $V_i$ ) is shown in Fig. 16. As expected,  $V_i$  magnitude changes between 0 and 150 V, respectively. Fig. 17 shows z-source network capacitor voltages. The voltage is equal to expected value of 125 V. Capacitor voltage is 0.5 ( $V_O + V_i$ ), as described in [5].

Fig. 15. (a) Output currents of nine-switch inverter (simulation). (b) Output currents of nine-switch inverter (experimental), (2 A/DIV, 10 ms/DIV).

Fig. 16. Output voltage of z-source network (simulation).

phase voltage of both outputs, respectively. The load current is seen in Fig. 20.

Number of switching of semiconductors for nine-switch inverter and z-source-nine-switch inverter using carrier-based PWM and the proposed SVMs are shown in Table VIII. Number of switching for 0.1 s with parameters of Table VII is calculated. As seen in Table VIII, number of switching is considerably reduced using proposed SVMs.

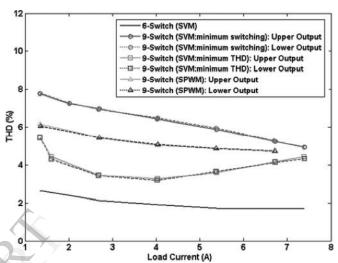

Fig. 21 shows THD of load current versus load current magnitude for four different cases: 1) carrier-based PWM, 2) minimum number of switching SVM, 3) reduced THD SVM, and 4) six switch inverter with SVM. Note that, for six switch inverter, dc bus voltage is set to 75 V, while for nine-switch inverters; dc bus voltage is set to 150 V. It is seen that the reduced THD SVM has best harmonic performance for nine-switch inverters. As seen in Fig. 21, six-switch inverter has better harmonic performance.

Fig. 17. (a) Capacitor voltage of nine-switch-z-source inverter (simulation). (b) Capacitor voltage of nine-switch-z-source inverter (experimental), (50 V/DIV, 1 ms/DIV).

Fig. 18. (a) Line voltage of nine-switch-z-source inverter (simulation). (b) Line voltage of nine-switch-z-source inverter (experimental), (50 V/DIV, 10 ms/DIV).

Fig. 19. (a) Phase voltage of nine-switch-z-source inverter (simulation). (b) Phase voltage of nine-switch z-source inverter (experimental), (50 V/DIV, 10 ms/DIV).

Fig. 20. (a) Output currents of nine-switch-z-source inverter (simulation). (b) Output currents of nine-switch-z-source inverter (experimental), (3 A/DIV, 10 ms/DIV).

TABLE VIII

NUMBER OF SEMICONDUCTOR SWITCHING

|                                   | SPWM | SVM<br>(Minimum<br>Switching) | SVM<br>(Minimum<br>THD) |

|-----------------------------------|------|-------------------------------|-------------------------|

| Nine-Switch<br>Inverter           | 3600 | 2400                          | 3400                    |

| Z-Source Nine-<br>Switch Inverter | 5400 | 2400                          | 3400                    |

Fig. 21. THD of load current of nine-switch inverter and six-switch inverter.

Main reason is that in nine-switch inverter, active vectors are not centered within the switching period.

## VII. CONCLUSION

In this paper, the SVM of nine-switch inverter and nine-switch-z-source inverter was proposed. Switching sequence of the proposed SVM is composed of the upper active vectors, the lower active vectors and the zero vectors. The upper and lower active vectors are determined via two space vector diagram. The proposed SVM increases sum of modulation indices up to 15%, an important feature in providing higher torque for a given input dc-voltage. The proposed SVM is also developed for nine-switch-z-source inverter via extra shoot-through vectors. For both inverters, two SVM algorithms are developed to reduce THD and number of semiconductor switching.

The proposed SVMs were simulated for both nine-switch inverter and z-source nine-switch inverter. An experimental setup was developed using a digital signal processor (DSP). The performance of the proposed SVMs was verified using computer simulation, and it was validated using experimental data.

www.ijert.org

8

## REFERENCES

- [1] T. Kominami and Y. Fujimoto, A novel nine-switch inverter for independent control of two three-phase loads,in Proc.IEEE Ind.Appl.Soc.Annu.Conf.(IAS),2007,pp.23462350.

- [2] C. Liu, B. Wu, N. Zargari, and D. Xu, A novel three-phase three-legAC/AC converter using nine IGBTs, IEEE Trans. Power Electron.,vol. 24, no. 5, pp. 11511160, May 2009.

- [3] C. Liu, B. Wu, N. Zargari, and D. Xu, A novel nine-switch PWM rectierinverter topology for three-phase UPS applications, J. Eur. Power Electron.(EPE), vol. 19, no. 2, pp. 110, 2009.

- [4] K. Oka, Y. Nozawa, R. Omata, K. Suzuki, A. Furuya, and K. Matsuse, Characteristic comparison between ve-leg inverter and nine-switch inverter, in Proc. Power Convers. Conf., Nagoya, 2007, pp. 279283.

- [5] F. Z. Peng, Z-source inverter, IEEE Trans. Ind. Appl., vol.39, no. 2,pp. 504510, Mar./Apr. 2003.

- [6] F. Z. Peng, M. Shen, and K. Holland, Application of Z-source inverter for traction drive of fuel cellbattery hybrid electric vehicles, IEEE Trans.Power Electron., vol. 22, no. 3, pp. 10541061, May 2007.

- [7] Y. Huang, M. Shen, and F. Z. Peng, A Z-source inverter for residential photovoltaic systems, IEEE Trans. Power Electron., vol. 21, no. 6,pp. 17761782, Nov. 2006.

- [8] S. M. Dehghan, M. Mohamadian, and A. Yazdian, A new variable speed wind energy conversion system using permanent magnet synchronous generator and Z-source inverter, IEEE Trans. Energy Convers., vol. 24,no. 2, Sep. 2009.

- [9] P. C. Loh, S. W. Lim, F. Gao, and F. Blaabjerg, Three-level Z-source inverters using a single LC impedance network, IEEE Trans. Power Electron., vol. 22, no. 2, pp. 706711, Mar. 2007.

- [10] P. C. Loh, F. Gao, and F. Blaabjerg, Topological and modulation design of three-level Z-source inverters, IEEE Trans. Power Electron., vol. 23, no. 5, pp. 22682277, Sep. 2008.[11] P. C. Loh, D. M. Vilathgamuwa, Y. S. Lai, and G. T. Chua, Pulse-with modulation of Z-source inverters, IEEE Trans. Power Electron., vol. 20, no. 6, pp. 13461355, Nov. 2005.

- [12] Y. Tang, S. Xie, C. Zhang, and Z. Xu, Improved Z-source inverter with reduced Z-source capacitor voltage stress and soft-start capability, IEEE Trans. Power Electron., vol. 24, no. 2, pp. 409415, Feb. 2009.

- [13] F. Z. Peng, M. Shen, and Z. Qian, Maximum boost control inverter, IEEETrans. PowerElectron., vol. 20, no. 4, pp. 833838, Jul. 2005.

**K.L.N.** Chaitanya received the Bachelor degree from Vasavi College of Engineering in Year 2010 and the Master degree from CMR College of Engineering and Technology in Year 2012. His research interests include applications of advanced electrical drives and power electronics.

K Srividya Savitri received the Bachelor degree from Sridevi Women's Engineering College in Year 2006 and the Master degree from Jawaharlal Nehru Technological University in Year 2009. She is currently working as Assistant Professor in the Department of Electrical and Electronics Engineering, CMR College of Engineering and Technology, Hyderabad. Her research interests include inverters, motor drives, inverter-based distributed generation, hybrid electric vehicle, and FACTS.

R. Shirisha received the Bachelor degree from SR Engineering College in Year 2006 and the Master degree from Vagdevi College of Engineering in Year 2011. She is currently working as Assistant Professor in the Department of Electrical and Electronics Engineering, CMR College of Engineering and Technology, Hyderabad. Her research interests include modeling, analysis, design and control of power electronic converters/system